## Design and Implementation of A Reversible Central Processing Unit

Lafifa Jamal

Registration No: 197

Session: 2014–2015

A Thesis submitted for the degree of Doctor of Philosophy in Computer Science and Engineering

Department of Computer Science and Engineering University of Dhaka, Dhaka-1000, Bangladesh

${\rm April}\ 2017$

## Declaration of Authorship

We declare that this thesis titled, 'Design and Implementation of a Reversible Central Processing Unit' and the works presented in it are my own. We confirm that:

- The full part of the work is done during PhD research study in University of Dhaka, Bangladesh.

- Any part of this thesis has not previously been submitted for a degree or any other qualification at this University or any other institution.

- We have consulted the published work of others with appropriate references.

- This thesis work is done by us and our contributions and enhancements from other works are clearly stated.

| igned:                              |  |

|-------------------------------------|--|

| Lafifa Jamal)                       |  |

| Candidate                           |  |

|                                     |  |

| Countersigned:                      |  |

| 0                                   |  |

| Professor Dr. Hafiz Md. Hasan Babu) |  |

| upervisor                           |  |

### Abstract

Reversible logic is an emerging technology. Conventional logic dissipates more power by losing bits of information whereas reversibility recovers bit loss from the unique input-output mapping. Reversible computing spans computational models that are both forward and backward deterministic. Reversible logic circuits require some constant ancilla inputs to generate the required functions. It produces some unused outputs, called garbage outputs, to maintain the reversibility of a circuit. It is important to minimize the number of ancilla inputs, number of garbage outputs and quantum cost in the design of reversible circuits. Reversible logic has promising applications in emerging computing paradigm such as quantum computing, DNA computing, optical computing, quantum dot cellular automata etc.

The central processing unit (CPU) is regarded as the brain of a computer. It is a piece of hardware that carries out the instructions needed to run a computer program. Processor speed determines the performance of a computer. It performs the basic arithmetical, logical, and input/output operations of a computer system. Advanced conventional processors have inherently higher power dissipation. The arithmetic logic unit of CPU performs simple arithmetic and logical operations and the control unit of CPU manages the various components of the computer.

Power dissipation is the main constrain when it comes to portability. Reversible logic gates are designed as a method to reduce the energy dissipation of logic circuits based on Launder's concept. Central processing unit designed using reversible logic have a significant contribution in low power computing.

Launder proved that a reversible circuit produces less power than the irreversible circuit. Moreover, by using power optimization algorithm, the power consumption of a reversible circuit can be optimized than their existing reversible counterparts. For example, for a 64-bit comparator, the proposed circuit achieves the improvement of 55.67% in terms of power over the existing reversible one.

Reversible circuit has some disadvantageous properties. It requires a large number of constant ancilla inputs. It also produces a large number of garbage outputs to maintain the reversibility which eventually increases the number of gates, area, power and delay. By using efficient design techniques and suitable algorithms

the number of garbage outputs should be minimized. For example, for a 64-bit comparator, the proposed circuit achieves the improvement of 33.1% in terms of garbage outputs over the existing reversible one.

As reversible computing is a new era in logic synthesis, the existing reversible central processing units have the lack of completeness. However, researchers proposed various basic components of reversible central processing unit. In this thesis, the basic elements of the reversible circuits are newly proposed or improved in terms of numbers of gates, garbage outputs, quantum cost and delay compared to the existing counterparts. The proposed reversible basic elements are further used to construct the complex circuits, such as memory circuits, arithmetic logic unit, control unit etc., in order to design a complete reversible central processing unit.

The main contribution of this thesis is to design a new reversible central processing unit which is efficient in terms of numbers of gates, garbage outputs, quantum cost, ancilla inputs and delay. The reversible central processing unit is designed using novel modularization approach by presenting architecture of a logically reversible processor based on the Von Neumann architecture that can operate with very low power consumption, protection of power analysis attack and long span of life due to less heat dissipation. The organization and architecture of the proposed processor is designed from scratch. Algorithms are proposed to produce the components of the reversible processor and to calculate area and power consumption. The capabilities of the new processor is determined, the datapath layout is designed and the necessary logic is constructed to control the datapath. The computational complexity is considered to estimate the execution time of the algorithm. Existing component designs are compared with the proposed components and theorems are presented to prove the superiority of the proposed architecture. The comparative results show that the proposed circuit requires less power than the existing circuits in terms of numbers of gates, garbage outputs, quantum cost, area and power. For example, for a 64-bit comparator, the proposed design achieves the improvement of 66.6% in terms of number of gates, 33.1% in terms of garbage outputs, 27.6% in terms of quantum cost, 52.39% in terms of area and 55.67% in terms of power over the existing reversible counterpart. The proposed components are simulated and the simulation results verify the correctness of the proposed design. The proposed reversible central processing unit can make a significant contribution in the field of low power reversible computing and quantum computing.

# This thesis is dedicated to the memory of my father

## Acknowledgements

Undertaking this PhD has been a truly life-changing experience for me and it would not have been possible to do without the support and guidance that I received from many people.

First and foremost I would like to thank my supervisor Professor Dr. Hafiz Md. Hasan Babu. It has been an honor to be his first PhD student. I would like to thank him for encouraging my research and for allowing me to grow as a research scientist. His advice on both research as well as on my career have been priceless. I truly appreciate all his contributions of time and ideas to make my PhD experience productive and stimulating. The joy and enthusiasm he has for his research was contagious and motivational for me, even during tough times in the PhD pursuit. I am also thankful for the excellent example he has provided as a successful researcher and professor.

I gratefully acknowledge the funding received towards my PhD from Prime Minister's Office. I received the PhD Fellowship of Prime Minister's Research and Higher Education Assistance Fund.

I would like to express my sincere gratitude to all the faculty members of Department of Computer Science and Engineering, University of Dhaka.

I owe a lot to family members, who encouraged and helped me at every stage of my personal and academic life, and longed to see this achievement come true. I love them so much, and I would not have made it this far without them. I specially acknowledge my mother for all her love and support. I dedicate this thesis to the memory of my father who would have been happy to see me to complete the degree.

Above all, I owe it all to Almighty Allah for granting me the wisdom, health and strength to undertake this research task and enabling me to its completion.

## Contents

| D            | eclar  | tion of Authorship                                                 | i            |

|--------------|--------|--------------------------------------------------------------------|--------------|

| $\mathbf{A}$ | bstra  | ${f t}$                                                            | i            |

| A            | cknov  | ledgements                                                         | $\mathbf{v}$ |

| Li           | ist of | Figures                                                            | ix           |

| Li           | ist of | Tables                                                             | кii          |

| 1            | Intr   | $\mathbf{duction}$                                                 | 1            |

|              | 1.1    | Problem Identification and Motivation towards Reversible Computing | 2            |

|              | 1.2    | Brief History of Microprocessor                                    | 5            |

|              |        | 1.2.1 Architecture of Intel 4004 Microprocessor                    | 8            |

|              |        | 1.2.2 Architecture of Pentium III Microprocessor                   | 10           |

|              |        | 1                                                                  | 12           |

|              |        | 1.2.4 Architecture of Core i5 Microprocessor                       | 14           |

|              |        | 1                                                                  | 15           |

|              | 1.3    | 3                                                                  | 19           |

|              | 1.4    | 8                                                                  | 20           |

|              | 1.5    | Outline of the Dissertation                                        | 21           |

| <b>2</b>     | Bas    | 1 0                                                                | 22           |

|              | 2.1    | Boolean Logic                                                      | 23           |

|              | 2.2    |                                                                    | 24           |

|              | 2.3    | Reversible Logic Gate                                              | 25           |

|              |        | 2.3.1 Garbage Output                                               | 25           |

|              |        | 2.3.2 Constant Input                                               | 26           |

|              |        | 2.3.3 Delay                                                        | 26           |

|              |        |                                                                    | 26           |

|              |        |                                                                    | 27           |

|              |        | 2.3.6 Quantum Cost                                                 | 27           |

|              |        | 2.3.7 Popular Quantum Gates                                        | 28           |

| $\frac{C\epsilon}{2}$ | onten                | ts            |           |                                                                        | vii |

|-----------------------|----------------------|---------------|-----------|------------------------------------------------------------------------|-----|

|                       | 2.4                  | 2.3.8<br>Summ | _         | Reversible Gates                                                       |     |

| 3                     | Lite                 | erature       | e Review  | v on Reversible Central Processing Unit                                | 38  |

|                       | 3.1                  |               |           | sible Arithmetic Logic Units                                           |     |

|                       | 3.2                  |               | 0         | sible Control Units                                                    |     |

|                       | 3.3                  |               | _         | sible Central Processing Unit                                          |     |

|                       | 3.4                  |               | _         |                                                                        |     |

| 4                     | $\operatorname{Pro}$ | posed         | Compo     | nents for Reversible CPU                                               | 48  |

|                       | 4.1                  | -             | -         | rsible Memory Components                                               |     |

|                       |                      | 4.1.1         |           | ed Reversible J-K Flip-Flop                                            |     |

|                       |                      | 4.1.2         | -         | ed Reversible Instruction Register                                     |     |

|                       |                      | 4.1.3         | Propose   | ed Reversible D Flip-Flop                                              | 53  |

|                       |                      | 4.1.4         | Propose   | ed Reversible Data Register                                            | 54  |

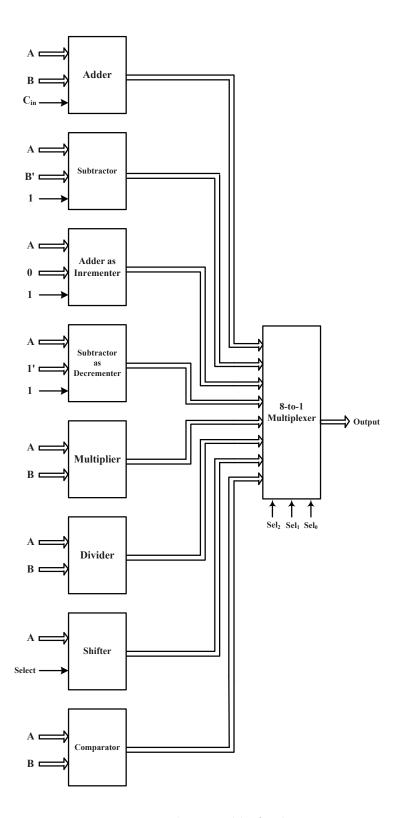

|                       | 4.2                  | Propo         | sed Desig | gns of the Components of Reversible Arithmetic Unit                    | 56  |

|                       |                      | 4.2.1         | Propose   | ed Reversible Carry Look-Ahead Adder                                   | 56  |

|                       |                      |               | 4.2.1.1   | Simulation of the Proposed Reversible Carry Look-Ahead Adder           | 60  |

|                       |                      |               | 4.2.1.2   | Performance Analysis of the Proposed Reversible Carry Look-Ahead Adder |     |

|                       |                      | 4.2.2         | Propose   | ed Reversible Divider                                                  |     |

|                       |                      | 1.2.2         | 4.2.2.1   | Proposed Reversible Divider using Conventional Division Array          |     |

|                       |                      |               | 4.2.2.2   | Proposed Reversible Divider using High Speed Division Array            |     |

|                       |                      |               | 4.2.2.3   | Performance Analysis of the Proposed Reversible Divider                |     |

|                       |                      | 4.2.3         | Propose   | ed Reversible Comparator                                               |     |

|                       |                      |               | 4.2.3.1   | Proposed Design of 1-bit Reversible Comparator Circuit                 |     |

|                       |                      |               | 4.2.3.2   | Proposed Design of Reversible MSB Comparator Circuit                   | 72  |

|                       |                      |               | 4.2.3.3   | Proposed Design of Reversible Single-bit Greater                       | . – |

|                       |                      |               | 1.2.0.0   | or Equal Comparator Cell                                               | 73  |

|                       |                      |               | 4.2.3.4   | Proposed Design of Reversible Single-bit Less Than Comparator Cell     |     |

|                       |                      |               | 4.2.3.5   | Proposed Design of Reversible 2-bit Comparator .                       | 74  |

|                       |                      |               | 4.2.3.6   | Proposed Design of Reversible $n$ -bit Comparator .                    |     |

|                       |                      |               | 4.2.3.7   | Performance Analysis of the Proposed Reversible Comparator             |     |

|                       |                      | 4.2.4         | Summa     | ry                                                                     |     |

|                       |                      |               |           |                                                                        |     |

| 5                     | _                    |               |           | of Proposed Reversible CPU                                             | 85  |

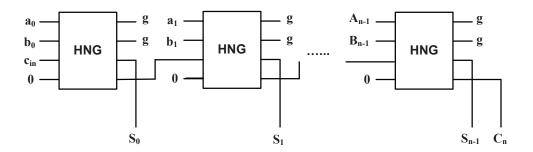

|                       | 5.1                  | Propo         | sed Desig | gn of the Reversible Arithmetic Logic Unit                             | 85  |

| $\frac{Ca}{C}$                          | Contents |                         |                                                                                 | viii  |

|-----------------------------------------|----------|-------------------------|---------------------------------------------------------------------------------|-------|

|                                         |          | 5.1.1<br>5.1.2<br>5.1.3 | Proposed Reversible Multiplexer                                                 | . 89  |

|                                         |          | 5.1.4                   | Proposed Reversible Arithmetic Logic Unit                                       |       |

|                                         | 5.2      | Propo                   | osed Reversible Control Unit                                                    |       |

|                                         |          | 5.2.1                   | Proposed Reversible Sequence Counter                                            |       |

|                                         |          | 5.2.2                   | Proposed Reversible Decoder                                                     |       |

|                                         |          |                         | 5.2.2.1 Proposed Reversible 2-to-4 Decoder                                      | . 103 |

|                                         |          |                         | 5.2.2.2 Proposed Reversible 3-to-8 Decoder                                      | . 104 |

|                                         |          |                         | 5.2.2.3 Proposed Reversible $n$ -to- $2^n$ Decoder                              | . 105 |

|                                         |          | 5.2.3                   | Proposed Reversible Control Gates                                               | . 107 |

|                                         |          | 5.2.4                   | Construction Procedure and Complexities of the Proposed Reversible Control Unit | . 108 |

|                                         |          | 5.2.5                   | Proposed Reversible Central Processing Unit                                     | . 110 |

|                                         |          | 5.2.6                   | Summary                                                                         | . 114 |

| 6                                       | Cor      | nclusio                 | ns and Future Works                                                             | 115   |

| Bi                                      | ibliog   | graphy                  |                                                                                 | 118   |

| Appendices Appendix A: List of Acronyms |          |                         |                                                                                 |       |

|                                         | App      | endix I                 | B: List of Publications                                                         | . 130 |

## List of Figures

| 1.1  | Intel 4004 Microprocessor Architecture [1]                                      |

|------|---------------------------------------------------------------------------------|

| 1.2  | Block Diagram of Intel Pentium III Microprocessor Architecture [2] 1            |

| 1.3  | Block Diagram of Intel Core i3 Microprocessor Architecture [3] 13               |

| 1.4  | Block Diagram of Intel Core i7 Microprocessor Architecture [3] 10               |

| 2.1  | An $n \times n$ Reversible Gate                                                 |

| 2.2  | Garbage Output of Reversible Feynman Gate                                       |

| 2.3  | Constant Input of Reversible Feynman Gate                                       |

| 2.4  | Quantum Realization of Reversible Fredkin gate                                  |

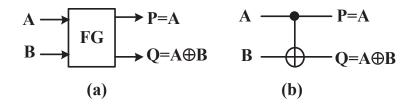

| 2.5  | Reversible Feynman Gate: (a) Block Diagram and (b) Quantum Realization          |

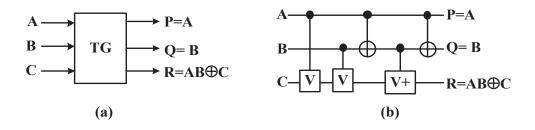

| 2.6  | Reversible Feynman Double Gate: (a) Block Diagram and (b) Quantum Realization   |

| 2.7  | Reversible Fredkin Gate: (a) Block Diagram and (b) Quantum Realization          |

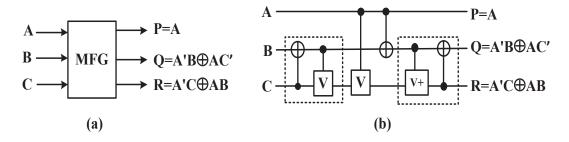

| 2.8  | Reversible Modified Fredkin Gate: (a) Block Diagram and (b) Quantum Realization |

| 2.9  | Reversible Toffoli Gate: (a) Block Diagram and (b) Quantum Realization          |

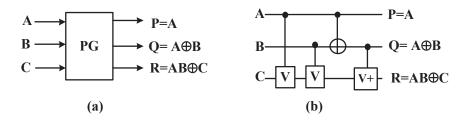

| 2.10 | Reversible Peres Gate: (a) Block Diagram and (b) Quantum Realization            |

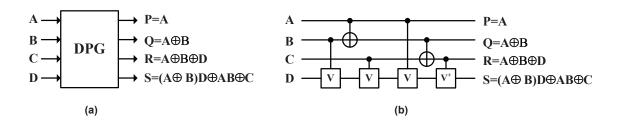

| 2.11 | Reversible Double Peres Gate: (a) Block Diagram and (b) Quantum Realization     |

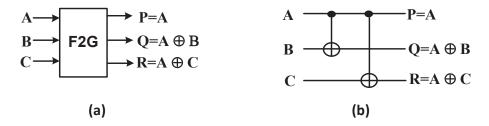

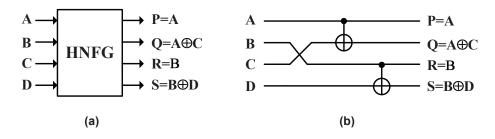

| 2.12 | Reversible HNFG Gate: (a) Block Diagram and (b) Quantum Realization             |

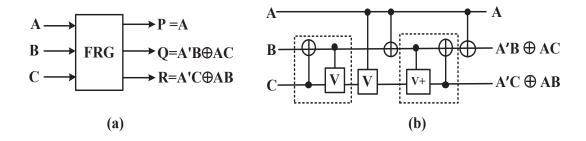

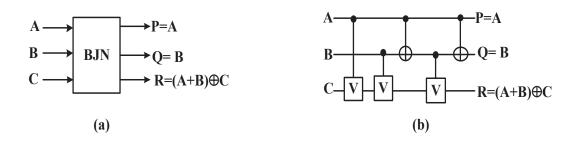

| 2.13 | Reversible BJN Gate: (a) Block Diagram and (b) Quantum Realization              |

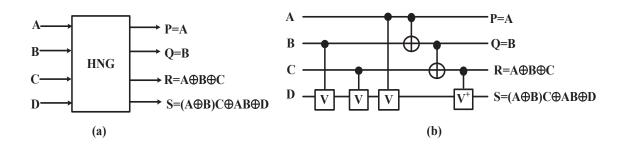

| 2.14 | Reversible HNG Gate: (a) Block Diagram and (b) Quantum Realization              |

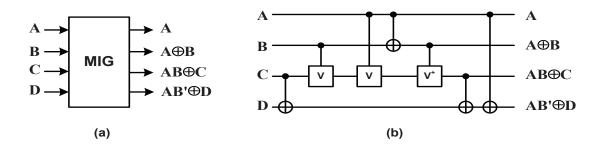

| 2.15 | Reversible MIG Gate: (a) Block Diagram and (b) Quantum Realization              |

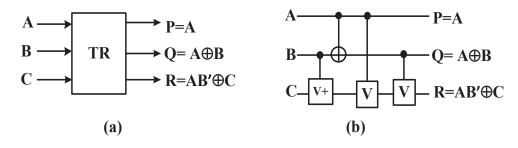

| 2.16 | Reversible TR Gate: (a) Block Diagram and (b) Quantum Realization 36            |

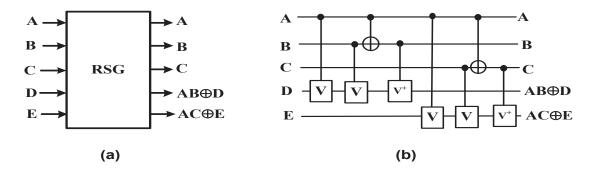

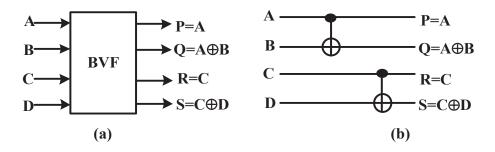

|      | Reversible RSG Gate: (a) Block Diagram and (b) Quantum Realization              |

| 2.18 | Reversible BVF Gate: (a) Block Diagram and (b) Quantum Realization              |

List of Figures x

| 3. | 1 RALU proposed by Zhou et al. [4]                                       | 39 |

|----|--------------------------------------------------------------------------|----|

| 3. |                                                                          | 40 |

| 3. |                                                                          | 40 |

| 3. |                                                                          | 41 |

| 3. | ,                                                                        | 42 |

| 3. |                                                                          | 42 |

| 3. |                                                                          | 43 |

| 3. | 8 RCPU proposed by Thomsen et al. [8]                                    | 44 |

| 3. |                                                                          | 45 |

| 3. | 10 RCPU proposed by Wille et al. [10]                                    | 46 |

| 3. |                                                                          | 46 |

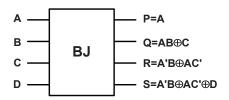

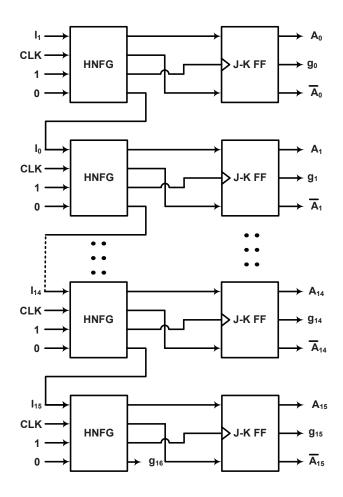

| 4. | G 1                                                                      | 49 |

| 4. | 2 NAND Implementation of BJ Gate                                         | 50 |

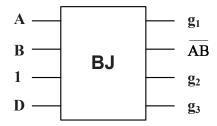

| 4. |                                                                          | 51 |

| 4. |                                                                          | 52 |

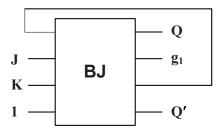

| 4. |                                                                          | 53 |

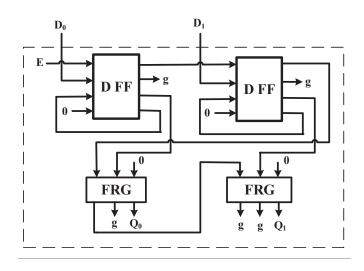

| 4. |                                                                          | 54 |

| 4. |                                                                          | 55 |

| 4. | 8 Proposed Reversible <i>m</i> -bit Register                             | 56 |

| 4. |                                                                          | 58 |

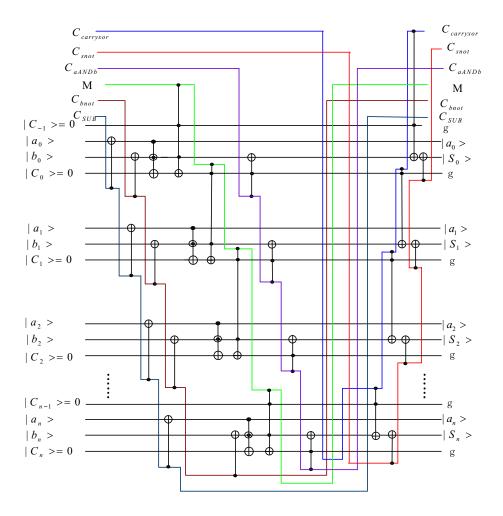

| 4. | 10 Proposed Reversible Carry Look Ahead Adder                            | 59 |

| 4. | 11 Simulation Result of Proposed Reversible 4-bit Carry Look-Ahead Adder | 61 |

| 4. |                                                                          | 62 |

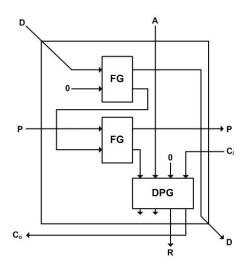

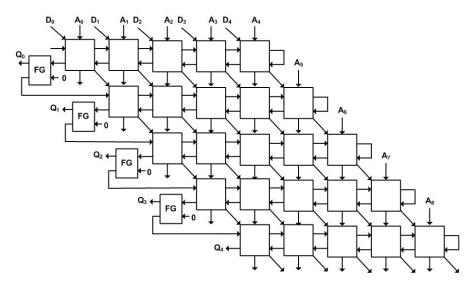

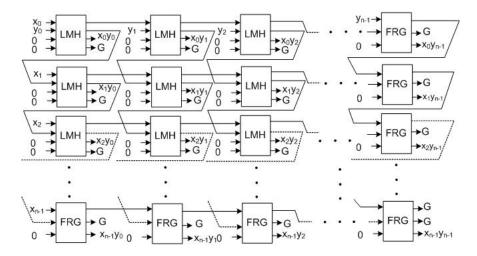

|    | 13 Proposed Reversible Conventional Division Array: 8-bit Dividend       |    |

|    |                                                                          | 63 |

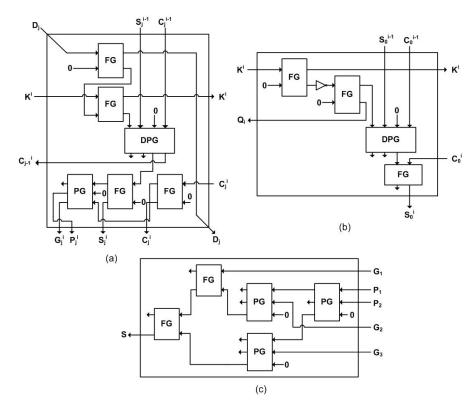

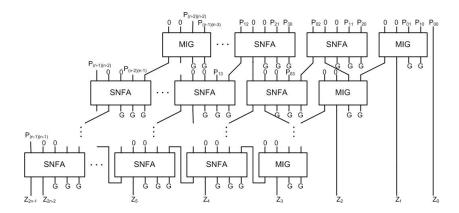

| 4. | 14 (a) A Cell; (b) S Cell; and (c) CLA Cell of Proposed High Speed       |    |

|    |                                                                          | 67 |

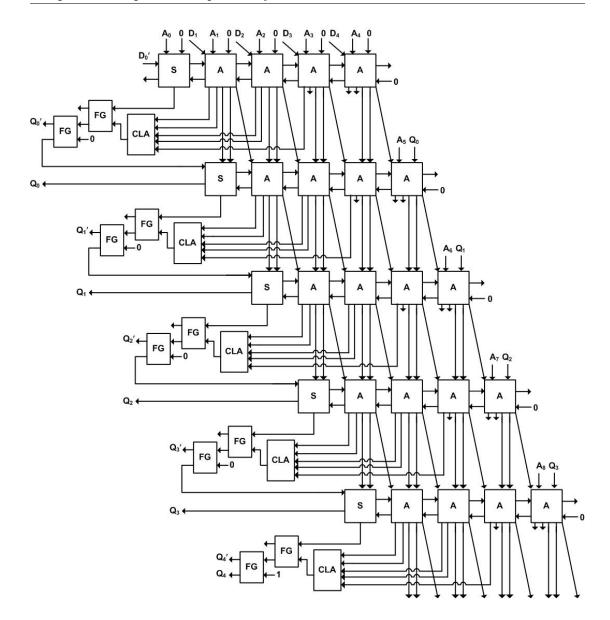

| 4. |                                                                          | 68 |

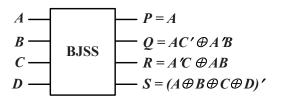

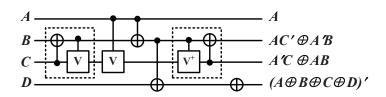

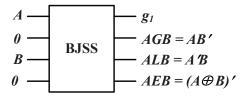

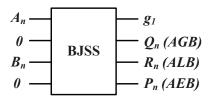

| 4. | 16 4×4 Reversible BJSS Gate                                              | 70 |

| 4. | 17 Quantum Realization of BJSS Gate                                      | 70 |

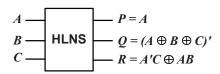

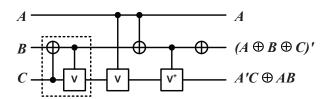

| 4. | 18 3×3 Reversible HLNS Gate                                              | 71 |

| 4. | 19 Quantum Realization of HLNS Gate                                      | 71 |

| 4. | 20 1-bit Reversible Comparator                                           | 72 |

| 4. | 21 MSB Comparator Circuit                                                | 73 |

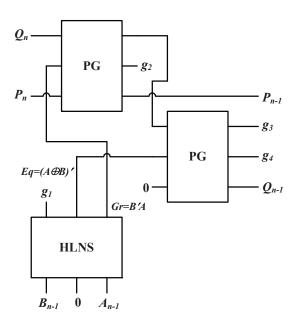

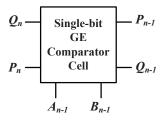

| 4. | 22 Proposed Design of Single-bit GE Comparator Cell                      | 73 |

| 4. | 23 Block Diagram of Single-bit GE Comparator Cell                        | 74 |

| 4. | 24 Proposed Design of Single-bit LT Comparator Cell                      | 74 |

| 4. | 25 Block Diagram of Single-bit LT Comparator Cell                        | 74 |

| 4. | 26 Proposed Design of Reversible 2-bit Comparator                        | 75 |

| 4. | 27 Proposed Design of Reversible $n$ -bit Comparator                     | 75 |

| 4. | 28 Simulation Result of Proposed Reversible 1-bit Comparator             | 82 |

| 4. | 29 Simulation Result of Proposed Reversible 2-bit Comparator             | 83 |

List of Figures xi

| 4.30 | Simulation Result of Proposed Reversible 4-bit Comparator 83               |

|------|----------------------------------------------------------------------------|

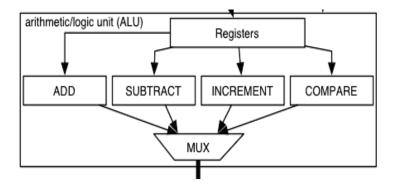

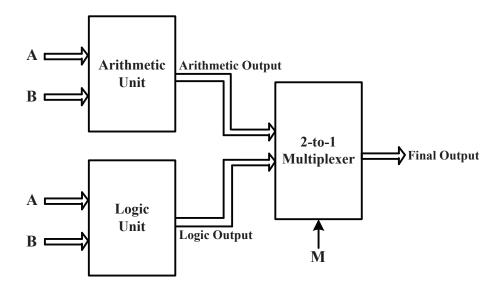

| 5.1  | Block Diagram of the Proposed Reversible Arithmetic Logic Unit . 86        |

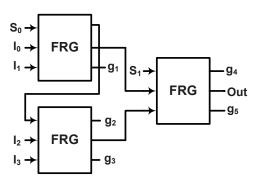

| 5.2  | Proposed 4-to-1 Reversible Multiplexer                                     |

| 5.3  | Timing Diagram of the Proposed 4-to-1 Reversible Multiplexer 88            |

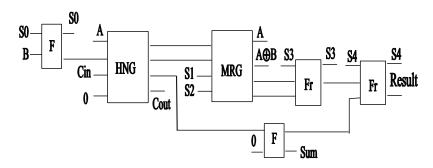

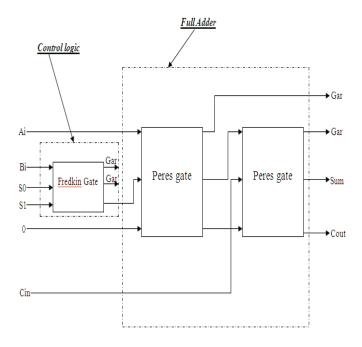

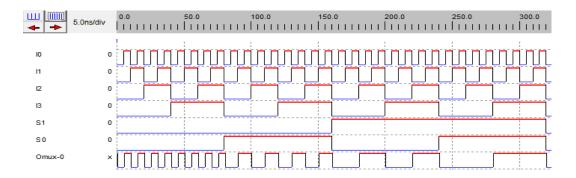

| 5.4  | Full adder using HNG gates [12]                                            |

| 5.5  | Proposed Reversible Arithmetic Unit                                        |

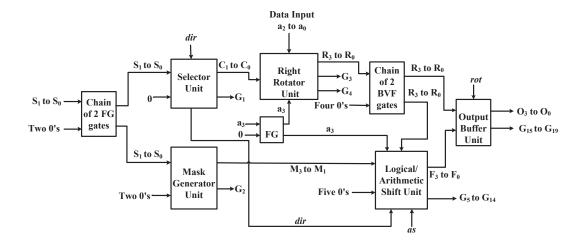

| 5.6  | Architecture of Partial Product Generation Circuit 92                      |

| 5.7  | Generalized Architecture of Multi-Operand Addition Circuit 92              |

| 5.8  | Block Diagram of Reversible Bidirectional Barrel Shifter 93                |

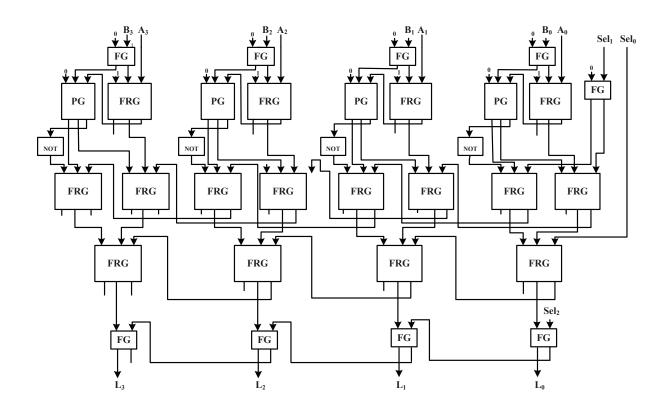

| 5.9  | Proposed Reversible Logic Unit                                             |

| 5.10 | Proposed Reversible Arithmetic Logic Unit                                  |

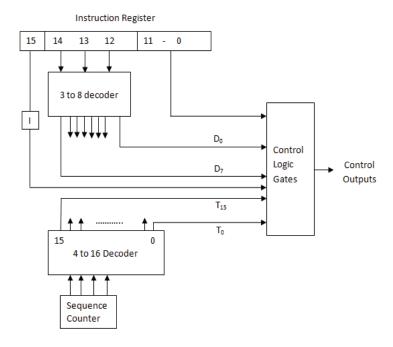

| 5.11 | Block Diagram of the Proposed Control Unit                                 |

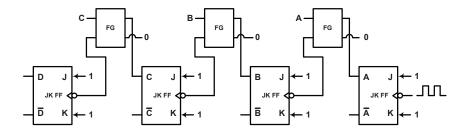

| 5.12 | Proposed Reversible Sequence Counter                                       |

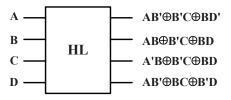

| 5.13 | Block Diagram of the Proposed Reversible HL Gate                           |

| 5.14 | Quantum Realization of the Proposed Reversible HL Gate $$ 102              |

| 5.15 | Proposed Reversible 2-to-4 Decoder                                         |

| 5.16 | Simulation Result of Proposed Reversible 2-to-4 Decoder 103                |

| 5.17 | Proposed Reversible 3-to-8 Decoder                                         |

| 5.18 | Proposed Reversible $n$ -to- $2^n$ Decoder                                 |

| 5.19 | Proposed Reversible Control Gates                                          |

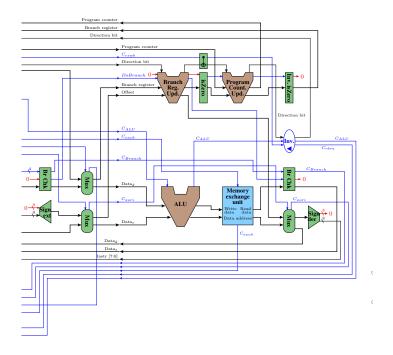

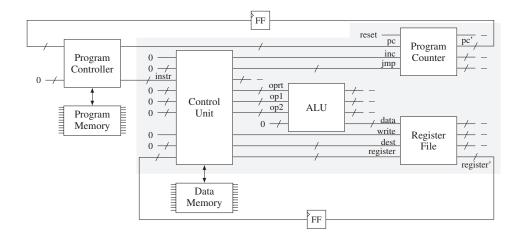

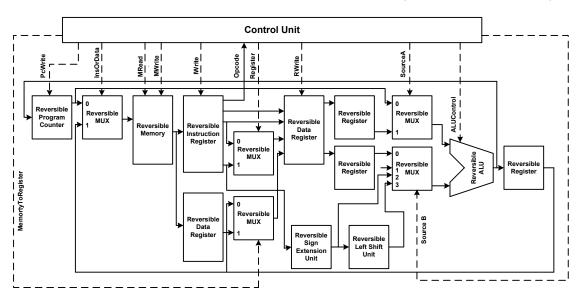

| 5.20 | Outline of the Design of the Proposed Reversible Processor 111             |

| 5.21 | Datapath Design of the Proposed Reversible Processor                       |

| 5.22 | Integrated Design of the Proposed Reversible Central Processing Unit . 113 |

## List of Tables

| 2.1  | Truth Table of a Boolean Function                                | 24  |

|------|------------------------------------------------------------------|-----|

| 2.2  | Truth Table of a Multiple Output Boolean Function                | 24  |

| 4.1  | Truth Table of 4×4 Reversible BJ gate                            | 50  |

| 4.2  | Comparison of Different J-K FFs                                  | 51  |

| 4.3  | Comparison of Different 16-bit Reversible Instruction Registers  | 52  |

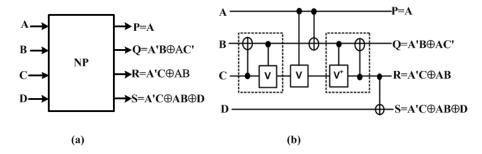

| 4.4  | Truth Table of 4×4 Reversible NP gate                            | 54  |

| 4.5  | Comparison of Reversible D FFs with $Q$                          | 55  |

| 4.6  | Comparison Reversible D FFs with $Q \& Q' \dots \dots$           | 55  |

| 4.7  | Comparison of Different 4-bit Reversible Carry Look-Ahead Adders | 61  |

| 4.8  | Comparison Between Proposed and Existing 2-bit, 4-bit, 8-bit and |     |

|      | 16-bit Dividers                                                  | 66  |

| 4.9  | Truth Table of $4\times4$ BJSS gate                              | 70  |

| 4.10 | Truth Table of $3\times3$ HLNS gate                              | 71  |

| 4.11 | Truth Table for 1-bit Binary Comparator                          | 72  |

| 4.12 | Comparison of Different Reversible $n$ -bit Comparators          | 83  |

| 4.13 | Area, Power and Delay Comparison of Different Reversible n-bit   |     |

|      | Comparators                                                      | 84  |

| 4.14 | Comparison of Different Reversible 8-bit Comparators             | 84  |

| 4.15 | Comparison of Different Reversible 64-bit Comparators            | 84  |

| 5.1  | List of operations of the Proposed Reversible ALU                | 86  |

| 5.2  | Comparison of Different 4-to-1 Reversible Mux                    | 89  |

| 5.3  | Comparison of Different Sequence Counters                        | 101 |

| 5.4  | Truth Table of 4×4 Reversible HL gate                            | 102 |

| 5.5  | Comparison of Different Reversible 2-to-4 Decoders               | 104 |

| 5.6  | Comparison of Different Reversible 3-to-8 Decoders               | 105 |

## Chapter 1

## Introduction

Since the beginning of time, technology has helped us out as a human race. From the invention of the wheel to the Internet, technology has greatly affected the way the civilization has grown. Our personal life is highly dependent on the technology that people have developed. Technology has advanced with years and it has influenced the way to live, communicate, travel. These continuous technological advancements have brought about many changes. As peoples demands and life style change, the demand for the type of technology to progress is very high. In the 20th and 21st centuries, the advancement in technology has been exceptionally fast. Over the last few decades, improvements in computer technologies have reached an impressive level. The central processing unit (CPU) has perhaps made more significant contributions to our daily lives than any other 20th-century invention. Now-a-days, the processor is not required only in desktop computers. Powerful CPUs are also required in portable and smart devices.

The central processing unit (CPU) is regarded as the brain of a computer [13]. It is a piece of hardware that carries out the instructions needed to run a computer program. It performs the basic arithmetical, logical, and input/output operations of a computer system. A CPU usually has a number of components. The first is the arithmetic logic unit (ALU), which performs simple arithmetic and logical operations. Second is the control unit (CU), which manages the various components of the computer. It reads and interprets instructions from memory and transforms

them into a series of signals which activate other parts of the computer. The control unit handles all processor control signals. It directs all input and output flow, fetches code for instructions from microprograms and directs other units and models by providing control and timing signals. Computer performance is primarily determined by the performance of the CPU.

Energy consumption is an important aspect of most computing systems today and this is especially true for embedded systems and battery-dependent computers. Reversible computing has the potential to reduce power consumption and heat dissipation [14], [15]. Reversible Central Processing Unit (RCPU) can play a significant role in designing portable and smart devices which requires extended battery life.

## 1.1 Problem Identification and Motivation towards Reversible Computing

Since the days of the mainframe and the desktop pc, processor technology has changed continually to address users' needs. During this era VLSI design efforts have focused primarily on optimizing speed to realize computationally intensive real-time functions. As a result, semiconductor ICs were invented to successfully integrated various complex modules to meet the computation demands. While these solutions have addressed the real-time problem, they have not addressed the increasing demand for portable operation. Now, with mobile computing becoming a dominant market, processor innovation has become a critical driving force for change. Power dissipation is the main constrain when it comes to portability. The portable device consumer demands more features and extended battery life at a lower cost. This requires high levels of integration in advanced processors, but advanced processors have inherently higher power dissipation. So, there is a need to reduce power dissipation to reduce power consumption.

Generally, the more expensive is the processor, the more it runs faster. This requires advanced processors which dissipates higher power. The basic elements of

quantum computers are the quantum gates. Reversible logic gates can be implemented using quantum gates. Preservation of information is a key motivation for research in reversible computing. Reversible logic gates are designed as a method to reduce the energy dissipation of logic circuits based on Launder's concept [15]. For this reason, the quantum computers dissipate very low power which eventually results low power consumption.

Nanotechnologies are the design, characterization, production and application of structures, devices and systems by controlling shape and size at nanometre scale [16]. Smaller, faster and lighter computers will be the potential result of the nanotechnology impact on computer technology. Conventional computers do not support nanotechnologies. So there is a need to introduce nanotechnologies in computer technologies. Nanotechnology may be used to develop many new kinds of batteries that are quicker-charging, more efficient, lighter weight, have a higher power density, and hold electrical charge longer. Smaller, faster and lighter nanotechnology based computers will have a significant impact on computer technology.

More powerful and smaller computers will encrypt data and provide round-the-clock security. Hardware cryptography utilizes the unique properties of quantum mechanics which provides unbreakable security for businesses, government, and military. Security of information is a vital issue. Software is not enough to protect a system. It also needs physical protection [17]. Despite the computation power, general purpose processors are not able to compete with dedicated crypto-processors for certain applications where information security must be entertained. Moreover, high-performance general purpose processors have enormous power consumption. They produce a tremendous amount of heat. Power dissipation and heat generation, make these processors almost unusable for embedded systems. The target of this thesis is to propose a new CPU with emerging technologies such as nanotechnologies, quantum technologies etc.

In this work, the design methodologies for the realization of reversible logic based central processing unit has been proposed. Reversible central processing unit is the foundation of a reversible computer. Implementation of reversible central processing unit can be a solution to reduce power consumption and to increase the performance of the whole system which leads to the main motivation of this thesis work. Reversible processor design is indeed a challenging task and thinking the organization and architecture of the design in reversible way requires a plenty of research works. Besides, previous works regarding reversible central processing unit lack efficiency and completeness. Hence, there is a scope of research to develop new design and methodology for realization of reversible central processing unit in which cost parameters are optimized.

Quantum computer is considered one of the most promising computing paradigm in which computation can be performed at an atomic level which makes it feasible to work beyond the existing limits of the semiconductor industry. A quantum computer is composed of quantum logic gates; each gate performing an elementary unitary operation on one, two or more two-state quantum systems called qubits. Each qubit represents an elementary unit of information corresponding to the classical bit values 0 and 1. Any unitary operation is reversible and hence quantum networks must be built from reversible logic components [18]. Reversible computers can easily be transformed into quantum computers. Thus, the feasibility of reversible logic circuits could critically impact in the realization of quantum computing. So, the efficient design of reversible computers leads us to construct the computers with the emerging technologies such as quantum computers, DNA computers etc. Moreover, energy dissipation would not occur if a computation is carried out in a reversible way [19]. The basic elements of reversible gates are quantum gates. So, the quantum computers, which are made of quantum gates, can play a significant role in the paradigm of low power computer devices. In contrast, there are emerging nanotechnologies such as Quantum Dot Cellular Automata (QCA) Computing, Optical Computing, and DNA Computing etc. [20], [21], [22], [23], [24] where the energy dissipated due to information destruction will be a significant factor of the overall heat dissipation of the system. Thus, one of the primary motivation for adopting reversible logic lies in the fact that it can provide a logic design methodology for designing ultra-low power circuits beyond KTln2 limit for those emerging nanotechnologies in which the energy dissipated due to information destruction will be a significant factor of the overall heat dissipation.

The performance of any computing system is given by the number of useful operations per unit time. The improving system performance requires increasing the average energy efficiency of useful operations which can be done by minimizing the energy dissipated during a job. Thus, in emerging nanotechnologies in which the signal energy is few orders of magnitude higher than the  $KT\ln 2$  limit (where K is the Boltzmann constant and T is the operating temperature), further improvements can only be gained by going beyond the  $KT\ln 2$  which is only possible by adopting the reversible logic. This shows that reversible logic can be beneficial towards raising computer performance in emerging nanotechnologies. Reversible logic could also help to potentially recover and retain a fraction of the signal energy that can be reused for subsequent operations by doing the computation using the forward path and then undoing the computation using the backward path. These concepts have been implemented in CMOS to save significant amount of energy dissipation even close to 90% using the concepts such as reversible energy recovery logic [25].

Reversible logic have also promising applications in online and offline testing of faults. For example, it has been proved by researchers that for reversible logic circuits, the test set that detects all single stuck-at faults can also detect multiple stuck-at faults [26].

In summary, the motivations for this dissertation are: (i) to explore the design and synthesis of reversible central processing unit considering metrics of numbers of reversible gates, garbage outputs, quantum cost, delay and ancilla inputs, and (ii) to explore the benefits of reversible logic in circuits based on emerging nanotechnologies.

To propose the new CPU, the existing processor technologies need to be studied. Section 1.2 discusses the brief history and architectures of different microprocessors.

#### 1.2 Brief History of Microprocessor

The first microprocessor, Intel 4004, was introduced in 1971 [27]. This processor could work with 4-bit at a time and run at a clock speed of 108KHz. It had

2,300 transistors and was built on a 10-micron process. The maximum address-able memory was 640 bytes. It was originally designed for use in a calculator. However, it proved to be useful for many other functions because of its inherent programmability.

8008 processor was introduced in 1972 [28]. It could run at a clock speed of 200KHz and it had 3,500 transistors. The big change in the 8008 was that it could move data 8-bit at a time, twice as much as the previous chip. It could also address 16KB memory. This chip was mainly used in dumb terminals and general-purpose calculators.

In 1974, 8080 processor was introduced [28]. It ran at a clock rate of 2 MHz. Its performance was 10 times better than the performance of the 8008. The 8080 chip, which contained 6,000 transistors, was built on a 6-micron process. As it had an 8-bit data bus, it could transfer 8 bits of data at a time. The 8080 could address up to 64KB of memory. Since this was the first processor chip used in the first personal computer, the Altair 8800, it initiated the PC revolution

Z-80 processor was the first clone processor. It was a vastly improved version of the 8080. The Z-80 also incorporated a superset of 8080 instructions. It could run all 8080 programs. In addition, it also included new instructions and new internal registers. Initially, the Z-80 ran initially at 2.5MHz. It contained 8,500 transistors and could access 64KB of memory.

The 8085 was released by Intel in 1976 [29]. It was popular as an embedded controller, finding use in scales and other computerized equipment. The 8085 ran at 5MHz and contained 6,500 transistors. It was built on a 3-micron process and incorporated an 8-bit data bus.

In 1976, MOS Technologies were introduced in 6502 microprocessor. It was an 8-bit processor. This chip was used in the designs of Apple I and Apple II. The 6502 and its successors were also used in game consoles, including the original Nintendo Entertainment System (NES).

In 1978, Intel introduced the 8086 [28]. The 8086 chip brought with it the original x86 instruction set that is still present in current x86-compatible chips such as the Pentium 4 and AMD Athlon. The 8086 could work on 16-bit numbers and data

internally and also transfer 16 bits at a time in and out of the chip. The 8086, which initially ran at up to 5 MHz, contained 29,000 transistors. It used 20-bit addressing. Although the 8086 was a great chip, its disadvantage was that it was expensive at the time. Moreover, it required expensive 16-bit board designs and infrastructure to support it.

Intel released 8088 processor in 1979. It used the same internal core as the 8086, had the same 16-bit registers, and could address the same 1MB of memory. However, the external data bus was reduced to 8 bits. This enabled support chips from the older 8-bit 8085 to be used, and far less expensive boards and systems could be made. These are the reasons why IBM chose the 8088 instead of the 8086 for the first PC.

Intel introduced the IA-64 (Intel Architecture, 64-bit) in the form of the Itanium and Itanium 2 processors. It was first announced in 1994 as a CPU development project with Intel and HP, and the first technical details were made available in October 1997. This resulted in the IA-64 architecture and Itanium chip, which was officially released in 2001.

AMD developed 64-bit extensions to IA-32, which it calls AMD64 (originally known as x86-64). Intel eventually released its own set of 64-bit extensions, which it calls EM64T or IA-32e mode.

The latest development is the introduction of dual-core processors from both Intel and AMD. Dual-core processors have two full CPU cores operating off of one CPU package. It allows a single processor to perform the work of two processors like multiple single-core processors, dual-core processors, split up the workload caused by running multiple applications at the same time. Current dual-core processors also support AMD64 or EM64T 64-bit extensions, which allows the user to enjoy both dual-core and 64-bit computing's advantages.

Modern desktop computers support systems with multiple CPUs. Both Intel and AMD currently offer fast quad, hex and octa-core desktop CPUs, making multi-CPU systems obsolete for many purposes. The desktop market has been in a transition towards quad-core CPUs since Intel's Core 2 Quad was released and are now common, although dual-core CPUs are still more prevalent.

#### 1.2.1 Architecture of Intel 4004 Microprocessor

The basic function of a CPU is to fetch, decode and execute instructions from memory. To accomplish this it fetches data from an external memory source and transfer it into the register. It can distinguish between instructions and operands. The CPU also performs additional tasks such as responding to external events such as resets and interrupts, provide memory management facilities to the operating system, etc. In brief, the CPU can do following operations: 1. Provide temporary storage for addresses and data 2. Perform arithmetic and logic operations 3. Control and schedule all operations

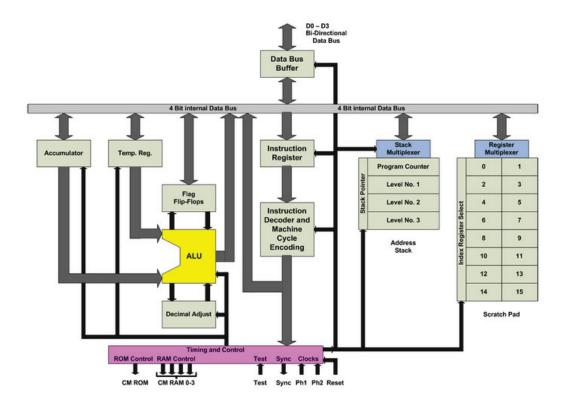

Figure 1.1 shows the basic architecture of Intel 4004 Microprocessor.

FIGURE 1.1: Intel 4004 Microprocessor Architecture [1]

The Intel 4004 microprocessor is consists of some basic elements which are instruction register, stack pointer, instruction decoder, program counter, accumulator register, flag register, arithmetic logic unit and control unit [1], [28].

Registers: Registers are used for a variety of purposes such as holding the address of instructions and data, storing the result of an operation, signaling the result of a logic operation, or indicating the status of the program or the CPU itself. They consist of several integrated transistors which are configured as a flip-flop circuits each of which can be switched into a 1 or 0 state. In order to provide backward compatibility, registers may be sub-divided. For example, the Pentium processor is a 32-bit CPU, and its registers are 32 bits wide. Some of these are sub-divided and named as 8-bit and 16-bit registers in order to run 8-bit and 16-bit applications designed for earlier x86 microprocessors.

**Instruction Register:** Instruction Register is a register which holds the instruction that is currently on execution. When the Bus Interface Unit receives an instruction it transfers it to the Instruction Register for temporary storage.

Stack Pointer: Stack registers are used when system calls are made by a process to operating system routines; or when hardware interrupts generated by input/output (I/O) transactions on peripheral devices; or when a process initiates an I/O transfer; or when a process rescheduling event occurs on foot of a hardware timer interrupt. The stack pointer is the register which holds the address of the most recent stack entry.

**Instruction Decoder:** Instruction Decoder decodes the instruction so that related microcode modules can be transferred from the CPU's microcode ROM to the execution unit. The Instruction Decoder also initiates the store of referenced operands in appropriate registers so data at the memory locations referenced can be fetched.

**Program Counter:** The Program Counter (PC) is the register that stores the address in primary memory of the next instruction to be executed. When the referenced instruction is fetched, the address in the PC is incremented to the address of the next instruction to be executed.

Accumulator Register: The accumulator may contain data to be used in a mathematical or logical operation, or it may contain the result of an operation. General purpose registers are used to support the accumulator by holding data to be loaded to/from the accumulator.

Flag Register: Each bit in the Flag register has a pre-assigned meaning and the contents are monitored by the control unit to help control CPU related actions.

Arithmetic and Logic Unit: The Arithmetic and Logic Unit (ALU) performs all arithmetic and logic operations in a microprocessor, e.g., addition, subtraction, logical AND, OR, EX-OR, etc. A typical ALU is connected to the accumulator and general purpose registers and other CPU components that help transfer the result of its operations to RAM via the Bus Interface Unit and the system bus.

Control Unit: The control unit coordinates and manages CPU activities, in particular the execution of instructions by the arithmetic and logic unit (ALU). In Pentium processors its role is complex, as microcode from decoded instructions are pipelined for execution by two ALUs.

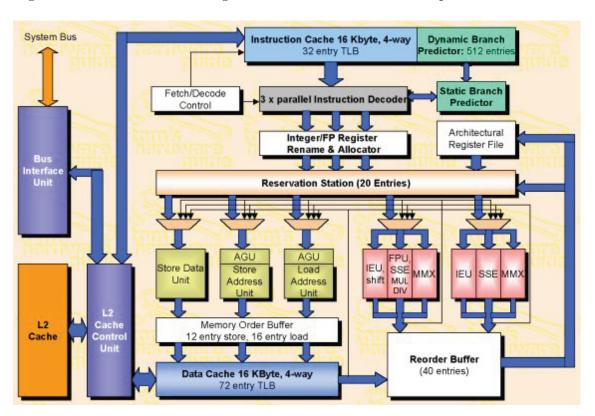

#### 1.2.2 Architecture of Pentium III Microprocessor

The Pentium III model, which was introduced in 1999, represents Intel's 32-bit x86 desktop and mobile microprocessors in accordance with the sixth-generation P6 micro-architecture. The Pentium III processor included SDRAM, which enabled incredibly fast data transfer between the memory and the microprocessor. Pentium III was also faster than its predecessor, the Pentium II, featuring clock speeds of up to 1.4 GHz. The Pentium III included 70 new computer instructions which allowed 3-D rendering, imaging, video streaming, speech recognition and audio applications to run faster. It has 512KB L2 Cache. It implements a Dynamic Execution microarchitecture a unique combination of multiple branch prediction, data flow analysis, and speculative execution. This enables these processors to deliver higher performance than the Intel Pentium processor, while maintaining binary compatibility with all previous Intel architecture processors. The processor also executes Streaming SIMD (single-instruction, multiple data) Extensions for enhanced floating point and 3-D application performance [2].

The processor utilizes multiple low-power states such as Sleep, and Deep Sleep to conserve power during idle times. The processor includes an integrated on-die 512KB 8-way set associative level-two (L2) cache. The L2 cache implements the Advanced Transfer Cache architecture with a 256-bit wide bus. In addition, the processor includes a 16 KB level one (L1) instruction cache and 16 KB L1 data cache. These cache arrays run at the full speed of the processor core. It has a dedicated L2 cache bus, thus maintaining the dual independent bus architecture to deliver high bus bandwidth and performance. Memory is cacheable for 64 GB of addressable memory space, allowing significant headroom for desktop systems. It supports a lower voltage differential and single-ended clocking for the system bus.

Figure 1.2 shows the block diagram of Intel Pentium III microprocessor.

FIGURE 1.2: Block Diagram of Intel Pentium III Microprocessor Architecture [2]

#### 1.2.3 Architecture of Core i3 Microprocessor

Core i3 microprocessor was introduced in 2010. The features of the i3 processor are highly improved as compared to previous version of the processor by Intel. Core i3 processors offer the perfect accuracy and high performance and response rate, as a result of which it provides the users with the high throughput rates, and also reduced time in executing the programs by the processor.

Core i3 processors offer the perfect accuracy and high performance and response rate which in result provide the users with the high throughput rates, and also reduced time in executing the programs by the processor. It is fully equipped by the latest HD graphics with powerful and advanced video engine that provides smooth high quality display along with the 3d graphics capabilities. On the whole i3 processors can be considered as the high graphical and multi media display processors for daily computing. Intel i3 processors also provide hyper threading technology to its users which enable the multitasking capability of both user and the system. The systems with i3 processors can perform execution and compilation of two tasks simultaneously without causing the executing delays and debuggers errors. i3 processors are smarter, faster and more adaptive in all kinds of networking scheme. They can be used with any of the hard disk configurations. Core i3 processors have 3.06 GHz and 2.93 GHz core speed which is very high as compared to the previous configurations of Intel processors. They have four processing threads that enables multithreading and multi tasking. 4 mega byte additional Cache memory is also provided inside the processor.

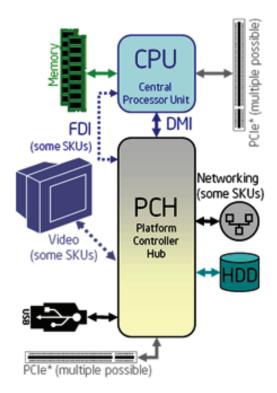

FIGURE 1.3: Block Diagram of Intel Core i3 Microprocessor Architecture [3]

Figure 1.3 shows the block diagram of Intel Core i3 microprocessor. It has several notable features, including:

- Dual core processing has the ability to run two independent programs with one hardware.

- i3 processors have improved Pentium base, they have totally new architecture with more integrations and high speed performance structure.

- Hyper threading technology also enables user to enjoy the high speed and better performance with more reliable outputs. It has 4 tasking threads that allows user to easily execute 3 to 4 programmes at a time.

- Smart memory and cache sequence allows user to enjoy the optimized and efficient data access both direct and sequentially. Effective shortcuts have reduced the access time of the file and system.

- HD graphical features also make these processors distinguished from the others because they are considered as best in their resolution.

#### 1.2.4 Architecture of Core i5 Microprocessor

Core i5 processors are more advanced as compared to the i3 or all the previous versions of the processors. Core i5 processors are introduced to do the intelligent networking and enhance the performance of the working for the sake of different purposes such as for gaming, faster procession, reliable data transmission etc. One of the important feature of the i5 processors is that it automatically manages the power supply where needed and does not break the speed and the performance of the system. They also allow the user to enjoy the heavy applications with the higher rate such as HD video composing, composing a music and many more. Core is also provide the opportunity to the users to use the system with multi tasking. They are also able to increase the memory of the system and help users to work with the high bandwidth and great performance. A big feature of the i5 processors is that they have ability to run two multitasking processors together that are generally called as dual processors and can increase the working performance of the system efficiently. Turbo boost technology of i5 processors is the key beneficial feature of the i5 processors that allow the users to do their regular and important working with the help of heavy applications. Core i5 processor also consists of Hyper Threading technology that enables the users for multitasking and improves their business or working by working on the two different tasks at the same time.

The features of Core i5 Microprocessor are listed below:

- Core i5 processors have ability to work with integrated memory and can enhance the performance of the applications. The increase the memory up to 1333 MHz.

- Core i5 processors have high speed performing rate so they are able to perform at the maximum CPU rate of 3.6 GHz.

- Turbo technology is present in the device that boost up the working speed of the computational systems.

- It also provides the 64-bit architecture for the users for the reliable and much more faster working.

- Micro architecture for the i5 processors was presented by the Nehalem and these processors have a cache rate up to 8 MB.

- It provides high quality visualization for advanced applications.

- It introduces high performance with the help of dual processor technology.

- The HD graphics enhance the video graphing and applications related to the same architecture.

#### 1.2.5 Architecture of Core i7 Microprocessor

The revolution of computer system has moved up enormously. From the age of heavy, bulky and large sized computers today the world has moved to thinnest notebooks. From the era of simple 4-bit Intel 4004 processors, we have moved up to Intel Core i7 [3].

Intel's Core i7 microprocessor is the latest and fastest microprocessor. Intel core i7 processor is one of the first core i-series processors built based on the new Intels micro architecture technology called Nehalem. Intels Nehalem micro architecture has key features that outrank from previous processor technologies.

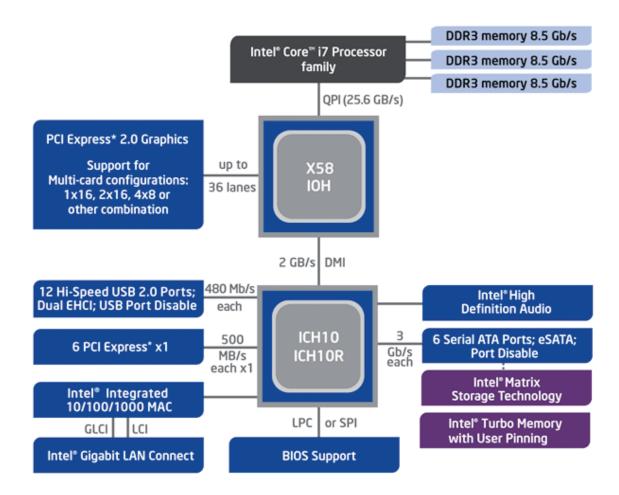

FIGURE 1.4: Block Diagram of Intel Core i7 Microprocessor Architecture [3]

Figure 1.4 shows the block diagram of Intel Core i7 microprocessor. It has several notable features, including:

- Four independent CPU cores

- 64-bit execution support

- Speed ranges from 2.66GHz to 3.33GHz

- Two-way multithreading per CPU core

- Front Side Bus Speed include 2GHz, 4.8GHz or 6.4GHz

- A built-in two-channel DDR3 DRAM controller

- Integrated L1, L2, and L3 caches

- Direct Media Interface (DMI) connection between the processor and the Platform Controller Hub (PCH)

- Enhanced Intel SpeedStep Technology

- Virtualization Technology

- Streaming SIMD Instructions (MMX)

- Over clocking capability

- Supports Intel Turbo Boost technology

The Intel Core i7 processor achieves its high performance through its multiple CPU cores and its Simultaneous Multithreading (SMT) feature. Between the four cores and the two-way multithreading per core, the Intel Core i7 processor appears to software as eight independent 64-bit CPUs [3].

The Core i7 design is based on current Core 2 processors but has been widely revised, from its front end to its memory and I/O interfaces and nearly everywhere in between. The Core i7 integrates four cores into a single chip, brings the memory controller onboard, and introduces a low-latency point-to-point interconnect called Quick Path to replace the front-side bus. Intel has modified the chip to take advantage of this new system infrastructure, tweaking it throughout to accommodate the increased flow of data and instructions through its four cores. The memory subsystem and cache hierarchy have been redesigned, and simultaneous multithreadingbetter known by its marketing name, Hyper-Threadingmakes its return, as well. The end result blurs the line between an evolutionary new product and a revolutionary one, with vastly more bandwidth and performance potential than other microprocessor in a single CPU socket.

Core i7 has almost 731 million transistors arranged into a 263  $mm^2$  area via the same 45nm, high-k fabrication process used to produce "Penryn" Core 2 chips. Penryn has roughly 410 million transistors and a die area of 107  $mm^2$  and it takes two Penryn dies to make one quad-core product.

Core i7 has large L3 shared cache memory. This L3 cache is the last level of a fundamentally reworked cache hierarchy. Inside of each core is a 32 kB L1 instruction cache, a 32 kB L1 data cache (it's 8-way set associative), and a dedicated 256

kB L2 cache (also 8-way set associative). Outside of the cores is the L3, which is much larger at 8 MB and smarter (16-way associative) than the L2s. The Core i7's cache setup differs from the Phenom's in key respects, though, including the fact that it's inclusive that is, it replicates the contents of the higher level cachesand runs at higher clock frequencies. As a result of these and other design differences, including a revamped TLB hierarchy, the Core i7's cache latencies are much lower than the Phenom's, even though its L3 cache is four times the size.

One mechanism Intel uses to make its caches more effective is prefetching [30], in which the hardware examines memory access patterns and attempts to fill the caches speculatively with data that's likely to be requested soon. Intel claims the Core i7's prefetching algorithm is both more efficient than Penryn's some server admins wound up disabling hardware prefetch in Xeons because it harmed performance with certain workloads, a measure Intel says should no longer be needed and more aggressive, as well.

The Core i7 can get to main memory very quickly which eliminates the chip-to-chip "hop" required when going over a front-side bus to an external north bridge. Officially, the maximum memory speed supported by the first Core i7 processors is 1066 MHz, which is a little conservative for DDR3, but frequencies of 1333, 1600, and 2000 MHz are possible with the most expensive Core i7, the 965 Extreme Edition.

With the memory controller onboard and the front-side bus, the Core i7 communicates with the rest of the system via the Quick Path interconnect (QPI). Quick Path is Intel's answer to Hyper Transport, a high-speed, narrow, packet-based, point-to-point interconnect between the processor and the I/O chip. The QPI link on the Core i7-965 Extreme operates at 6.4 GT/s. At 16 bits per transfer, that adds up to 12.8 GB/s, and since QPI links involve dedicated bidirectional pairs, the total bandwidth is 25.6 GB/s. Lower-end Core i7 processors have 4.8 GT/s QPI links with up to 19.2 GB/s of bandwidth.

This first, high-end desktop implementation of Nehalem is code-named Bloom-field, and it's essentially the same silicon that should go into two-socket servers eventually. As a result, Bloomfield chips come with two QPI links onboard, as the die shot above indicates. However, the second QPI link is unused. In 2P servers

based on this architecture, that second interconnect will link the two sockets, and over it, the CPUs will share cache coherency messages and data again.

In order to take advantage of this radically modified system architecture, the design team tweaked Nehalem's processor cores in a range of ways big and small. Although the Core 2's basic four-issue-wide design and execution resources remain more or less unchanged, almost everything around the execution units has been altered to keep them more fully occupied. The instruction decoder can fuse more types of x86 instructions together and, unlike Core 2, it can do so when running in 64-bit mode. The branch predictor's accuracy has been enhanced, too. Many of the changes involve the memory subsystemnot just the caches and memory controller but inside the core itself. The load and store buffers have been increased in size, for instance. A single Core i7 processor supports a total of eight threads.

The Core i7 processors series is recommended for multitasking, multithreading applications, extreme 3D gaming, creating professional movies and editing graphical tasks etc. [31]

#### 1.3 Objectives

The objectives of this thesis are as follows:

- To design a low cost Reversible Arithmetic Logic Unit (RALU).

- To construct a cost efficient Reversible Control Unit (RCU).

- To find an efficient technique to combine the RALU, RCU and other components to construct a low cost RCPU.

- To optimize the number of reversible gates, garbage outputs, quantum cost, area, power and delay of the RCPU by optimizing all of the individual components of RCPU.

#### 1.4 Methodologies of this Research

While working on this research, the following steps were followed:

- Studying the existing Reversible Central Processing Units (RCPU), Reversible Arithmetic Logic Units (RALU) and Reversible Control Units (RCU) and find the drawbacks of existing circuits.

- Proposing an overall block diagram of the RCPU which overcomes the problems of the existing RCPUs.

- Proposing the block diagram of the RALU.

- Designing the optimized individual circuits of the proposed RALU such as adder, subtractor, multiplier, divider, shifter, rotator, comparator, logical unit etc.

- Analyzing the proposed components in terms of cost and performance efficiency.

- Proposing the block diagram of the RCU.

- Proposing a new reversible gate to construct a cost effective Reversible Flip-Flop (RFF) which is used as the basic elements of the reversible memory circuits such as instruction registers and sequence counters.

- Proposing the cost effective designs of the individual elements of the proposed RCU such as decoders, counters, registers, control logic gates etc.

- Analyzing the proposed components in terms of cost and performance efficiency.

- Designing other components of the RCPU such as multiplexer, registers etc.

- Placing the proposed RALU, RCU and other components of the proposed RCPU efficiently and layout the optimized datapath which can handle all of the operations of the proposed RCPU.

- Realizing the overall architecture and organization of the proposed RCPU.

#### 1.5 Outline of the Dissertation

The remainder of this dissertation is organized as follows:

- Chapter 2 "Basic Concepts of Reversible Logic" provides the basic definitions and ideas of reversible logic. With this introductory part the reader becomes familiar with the objective and notations of reversible logic theory.

- Chapter 3 "Literature Review on Reversible Central Processing Unit" discusses the existing works on reversible arithmetic logic unit, reversible control unit and reversible central processing unit. It also describes the advantages and disadvantages of the existing works in literature.

- Chapter 4 "Proposed Components for Reversible CPU" presents the proposed designs of various components of the proposed reversible central processing unit. It presents the comparative analysis of proposed basic components with existing approaches and also includes simulation results.

- Chapter 5 "Implementation of Proposed Reversible CPU" presents the proposed designs of reversible arithmetic logic unit, eversible control unit and the datapath construction and integration method of the proposed RALU and RCU.

- Chapter 6 "Conclusions and Future Works" highlights the accomplishments and limitation of this work and points to the directions of further research in reversible logic area.

## Chapter 2

## Basic Concepts of Reversible Logic

Preservation of information is a key motivation for research in reversible computing. Reversible logic gates are designed as a method to reduce the energy dissipation of logic circuits based on Launder's [15] concept. In 1961, he stated that all logical operations are associated with a physical operation and since physical irreversibility requires heat generation, then so does logical irreversibility. According to Launder's [15] research, each bit of information loss necessitates at least  $KT\ln 2$  Joules of energy dissipation, where K is the Boltzmann constant and T is the operating temperature. In room temperature T, the amount of dissipating heat is small (i.e.  $2.9 \times 10^{-21}$  Joules), but not negligible. This amount may not seem to be significant, but it will become relevant in the future. According to Gordon Moore's [32] prediction, the heat dissipated by the device will be equal to a nuclear reactor by the end of 2050. The problem of power dissipation can be solved by preserving information which leads to the development of reversible logic. Moore's law predicts exponential growth of the heat generated due to the information loss, which will be a noticeable amount of heat loss in the next decade.

Arithmetic circuits play a crucial role in VLSI technology. Among various arithmetic circuits, multiplier and barrel shifter are two important circuits that can be realized with low power dissipation. Multiplier is very useful in many high performance systems such as FIR filters, microprocessors, digital signal processors

etc. A system's performance is mostly dependent on multiplier since it is regarded as the slowest element in the system. Shifter is another important circuit which is used in various applications such as floating point normalization, bit-indexing, variable-length coding etc. Usually digital signal processor and some high performance processors use barrel shifter which can shift multiple bits in a single cycle. This thesis presents logically reversible signed multiplier and bidirectional barrel shifter which do not erase a bit of information and as a result solve at least two problems: overheating and power saving.

This chapter presents the basic terminologies of reversible logic along with some popular reversible logic gates relevant to this research work. Illustrative figures and examples are included in respective sections.

#### 2.1 Boolean Logic

Boolean Logic is a form of algebra in which all values are in two forms: TRUE or FALSE. Boolean logic is specially important for computer science because it matches with the binary number system, in which each bit has a value of either 1 or 0. There are two Boolean constants, 0 and 1. Boolean algebra was introduced by the mathematician George Boole. A Boolean function  $f(x_1, x_2, ..., x_n)$  of n variables can be represented by a truth table with n input columns and one output column.

#### Example 2.1:

Let, F(A, B, C) = B + AC, where A, B and C are Boolean variables and F is the Boolean function. The output will be high if B = 1 or AC = 1 or both are 1. The truth table of this function is shown in Table 2.1. The number of rows in the truth table is  $2^n$  where n is the number of input variables (n = 3 for the given equation). Hence there are  $2^3 = 8$  possible input combination of inputs.

An *n*-input *k*-output multiple output Boolean function  $(f_1(x_1, x_2, ..., x_n); f_2(x_1, x_2, ..., x_n);$ ...;  $f_k(x_1, x_2, ..., x_n))$  can be represented in a truth table with (n+k) columns, where the last *k* columns represent the function output for the input pattern contained in the first *n* columns.

| A | B | C | F(A,B,C) |

|---|---|---|----------|

| 0 | 0 | 0 | 0        |

| 0 | 0 | 1 | 0        |

| 0 | 1 | 0 | 1        |

| 0 | 1 | 1 | 1        |

| 1 | 0 | 0 | 0        |

| 1 | 0 | 1 | 1        |

| 1 | 1 | 0 | 1        |

| 1 | 1 | 1 | 1        |

Table 2.1: Truth Table of a Boolean Function

#### Example 2.2:

Let, F1(A, B, C) = B + AC and F2(A, B, C) = ABC where A, B and C are Boolean variables and F1 and F2 are multiple output Boolean function. The truth table of this multiple output function is shown in Table 2.2. The number of rows in the truth table is  $2^n$  where n is the number of input variables (n = 3 forthe given equation). Hence there are  $2^3 = 8$  possible input combination of inputs. The number of columns in the truth table is (n + k) where, k is the number of output functions (k = 2 for the given equation).

F1(A, B, C)F2(A,B,C)ABC

Table 2.2: Truth Table of a Multiple Output Boolean Function

#### 2.2 Reversible Logic

The multiple output Boolean function  $F(x_1, x_2, ..., x_n)$  of n Boolean variables is called reversible if: 1. the number of outputs is equal to the number of inputs;

2. there is a one-to-one relationship between the input and output sets; In other words, reversible functions are those that perform permutations of the set of input vectors.

## 2.3 Reversible Logic Gate

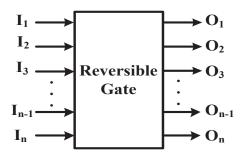

According to Kerntopf [33], a Boolean function is reversible if it maps each input assignment into a unique output assignment. So, an n-input n-output gate (circuit) is reversible if it realizes an  $n \times n$  reversible function [33]. If  $I_v = (I_1, I_2, ..., I_{n-1}, I_n)$  is the input vector and  $O_v = (O_1, O_2, ..., O_{n-1}, O_n)$  is the output vector, then an  $n \times n$  reversible gate (circuit) can be represented as  $I_v \leftrightarrow O_v$ . Figure 2.1 shows the realization of an  $n \times n$  reversible logic gate.

FIGURE 2.1: An  $n \times n$  Reversible Gate

#### 2.3.1 Garbage Output

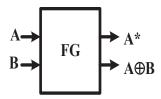

Garbage output is the information that is not needed for the computation [34]. More formally, every output of a gate that is not used as a input to other gate or as a primary output is considered as garbage output. For example, Feynman gate [35] can be used to perform Exclusive-OR between two inputs. In this case, one extra output will be generated which is the garbage output in this regard. The garbage output of Feynman gate is marked as \* in Figure 2.2.

FIGURE 2.2: Garbage Output of Reversible Feynman Gate

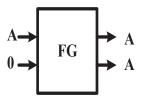

#### 2.3.2 Constant Input

In reversible circuits, some constant input bits are used in addition to the primary inputs to realize different logic functions which are referred to as ancilla inputs or constant inputs. The number of constant inputs should be minimum to design reversible logic circuits. Reversible Feynman gate [35] is used to copy an input when a constant 0 is fed to the second input as shown in Figure 2.3.

FIGURE 2.3: Constant Input of Reversible Feynman Gate

#### 2.3.3 Delay

The delay of any reversible logic gate can be computed by calculating its logical depth [36]. The logical depth corresponds to the number of quantum gates in a path. Reversible  $1 \times 1$  and  $2 \times 2$  gates have unit delay. The delay is denoted by  $\Delta$ . In this research work, logical depth is used as a measure of delay. For example, The Fredkin gate requires  $5\Delta$  delay as shown in Figure 2.4.

#### 2.3.4 Area

The area of a reversible logic circuit is the summation of individual area of each reversible gate of the circuit. Suppose, a reversible circuit consists of n reversible gates and area of those n gates are  $a_1, a_2, ..., a_n$ . Then by using above definition,

area (A) of that circuit is

$$A = \sum_{i=1}^{n} a_i$$

Given the above definition the area of a circuit can be calculated easily by obtaining area of each individual gate using CMOS 45 nm Open Cell Library [37].

#### 2.3.5 Power

The power of a reversible logic circuit is the summation of individual power of each reversible gate of the circuit. Suppose, a reversible circuit consists of n reversible gates and individual power of those gates are  $p_1, p_2, ..., p_n$ , respectively. Then, the power (P) of the circuit is

$$P = \sum_{i=1}^{n} p_i$$

The current rating of each gate can be obtained by using CMOS 45 nm Open Cell Library [37], Microwind DSCH 3.5 [38] and voltage is constant across each transistor, power requirement of each transistor can be calculated using the formula  $P = V \times I$ . Here, P refers to the power, V refers to the voltage and I refers to the current.

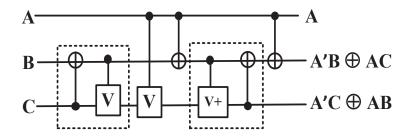

#### 2.3.6 Quantum Cost

One of the key challenges in reversible logic design is to optimize quantum cost of a reversible circuit. The quantum cost of a reversible gate (circuit) can be calculated by counting the number of elementary quantum gates required to realize the reversible function [39]. The quantum gates are inherently reversible and manipulates qubits [40]. Just as a classical bit has a state either 0 or 1, a qubit also has a state either  $|0\rangle$  or  $|1\rangle$  [39]. The state of a qubit can be expressed like  $|\psi\rangle = \alpha |0\rangle + \beta |1\rangle$ , where  $\alpha$  and  $\beta$  are complex numbers and denotes the probability of having the state  $|0\rangle$  or  $|1\rangle$ . The most used elementary quantum gates are the NOT gate [35] (a single qubit is inverted), the Controlled-NOT (CNOT) gate [35] (the target qubit is inverted if the control qubit is 1), the Controlled-V gate [40] (also known as a square root of NOT), and the Controlled

V+ gate [40] (performs the inverse operation of Controlled-V gate and thus is also a square root of NOT). The Controlled-V and Controlled-V<sup>+</sup> are  $1 \times 1$  gates having the following properties:

$$V \times V = NOT$$

$$V \times V^{+} = V^{+} \times V = I$$

$$V^{+} \times V^{+} = NOT$$

Here, I represents an identity and NOT represents an inverse operation. According to the quantum circuit shown in Figure 2.4, the quantum cost of a  $3 \times 3$  reversible Fredkin gate is 5 [41] as it requires two CNOT (marked as rectangular block), one Controlled-V and two NOT gates.

FIGURE 2.4: Quantum Realization of Reversible Fredkin gate

#### 2.3.7 Popular Quantum Gates

A quantum gate or quantum logic gate is a rudimentary quantum circuit operating on a small number of qubits. They are the analogues for quantum computers to classical logic gates for conventional digital computers. Quantum logic gates are reversible, unlike many classical logic gates. In this section, some popular quantum gates are defined formally with their input-output vectors and quantum realizations.

#### Pauli-X Gate (NOT Gate)

The Pauli-X gate acts on a single qubit [42]. It is equivalent to NOT gate. It maps  $|0\rangle$  to  $|1\rangle$  and  $|1\rangle$  to  $|0\rangle$ . It is represented by the Pauli Matrix is

$$X = \left[ \begin{array}{cc} 0 & 1 \\ 1 & 0 \end{array} \right]$$

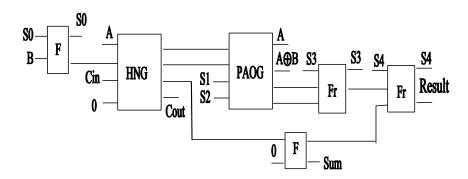

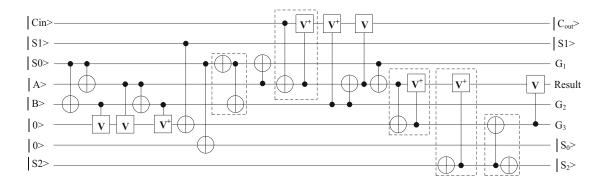

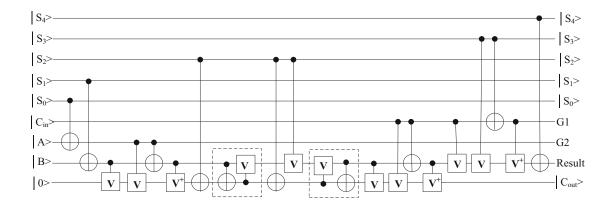

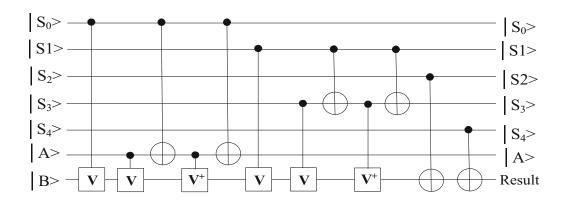

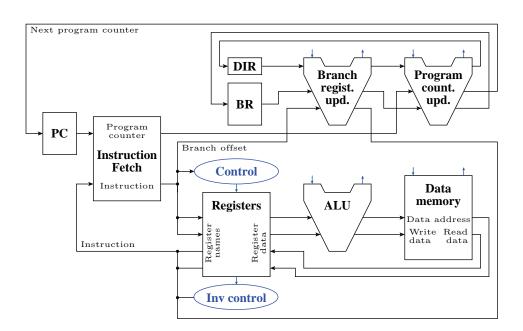

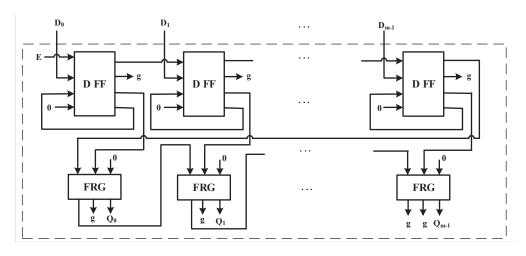

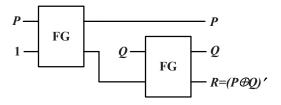

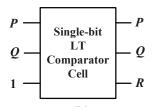

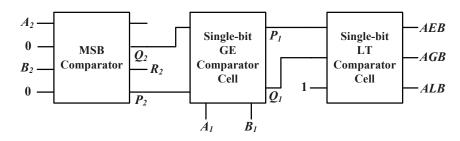

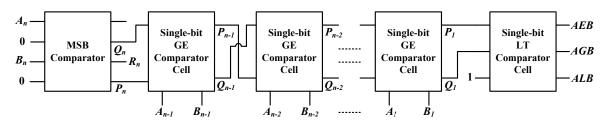

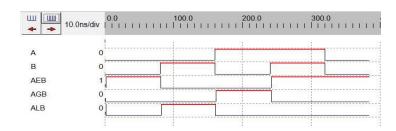

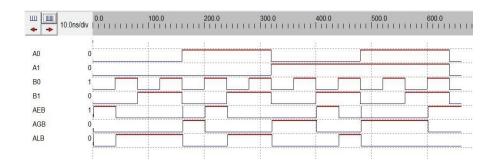

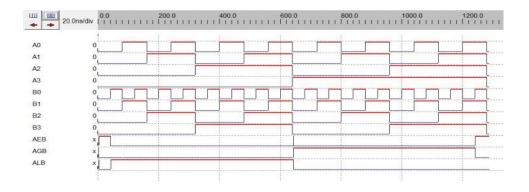

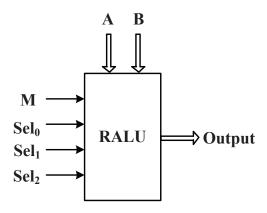

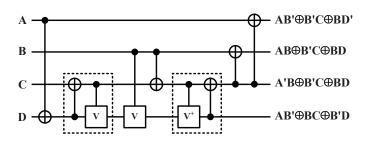

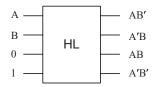

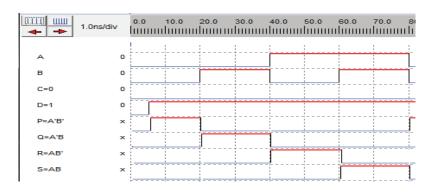

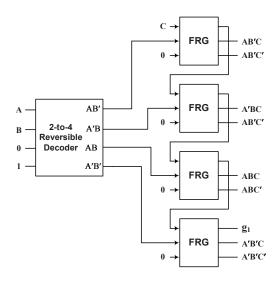

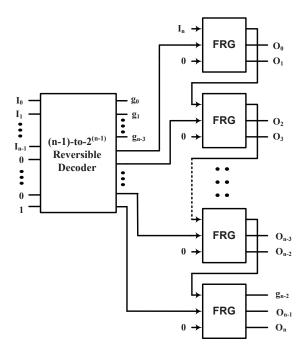

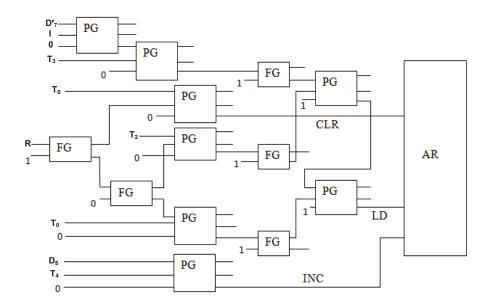

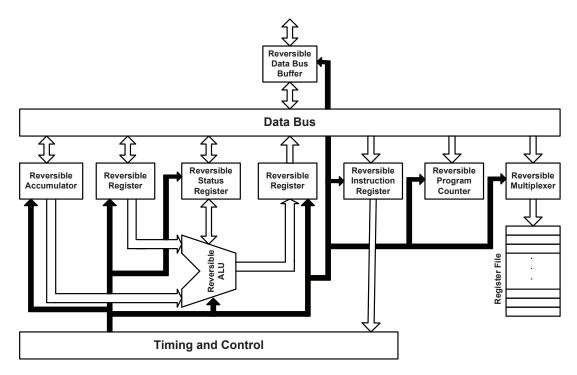

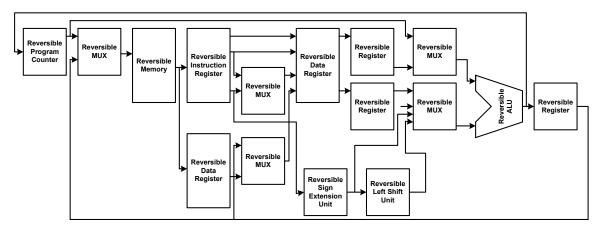

#### Controlled-NOT Gate