# Study on Structural, Optical and Electrical Properties of Single Junction Mono-crystalline Silicon Solar Cells

Ph. D. Thesis by

#### **Nahid Akter**

(Registration No. 138/2011-2012) Electrical and Electronic Engineering

In Partial Fulfilment of the Requirement for the Degree of

## **Doctor of Philosophy**

Under the supervision of

### Professor Dr. Zahid Hasan Mahmood

Electrical and Electronic Engineering University of Dhaka, Dhaka-1000, Bangladesh

### **Professor Dr. Nowshad Amin**

Electrical, Electronic and Systems Engineering Universiti Kebangsaan Malaysia (UKM) Bangi, Selangor 43600, Malaysia

June, 2017

# **Originality Statement**

I hereby declare that this submission is the own work of Ms. Nahid Akter and to the best of my knowledge it contains no materials previously published or written by another person, or substantial proportions of material which have been accepted for the award of any other degree or diploma at the University of Dhaka or any educational institution, except where due acknowledgement is made in the thesis. Any contribution made to the research by others, with whom Ms. Nahid Akter has worked at University of Dhaka or elsewhere, is explicitly acknowledged in the thesis. I also declare that intellectual content of this thesis is the product of Ms. Nahid Akter's research work, except to the extent that assistance from others is acknowledged.

Supervisor

Professor Dr. Zahid Hasan Mahmood

Dept. of Electrical and Electronic Engineering

University of Dhaka, Dhaka-1000, Bangladesh

Co-supervisor

Professor Dr. Nowshad Amin

Novimed Ann

Dept. of Electrical, Electronic and Systems Engineering

Faculty of Engineering and Built Environment

Universiti Kebangsaan Malaysia (UKM)

Bangi, Selangor 43600, Malaysia

# Acknowledgements

This entire research work has been carried out in the Institute of Electronics, Atomic Energy Research Establishment, Dhaka Bangladesh during the period of January 2014 to July 2015 as a 'Visiting Ph.D. Student' and Solar Energy Research Institute (SERI), Department of Electrical, Electronic and Systems Engineering, Faculty of Engineering and Built Environment, Universiti Kebangsaan Malaysia during the period August 2015 to September 2015 as a 'Visiting International Ph.D. Student'.

I wish to express my deepest gratitude towards my supervisor, Professor Dr. Zahid Hasan Mahmood. He navigated me to keep my perspective and focus in the right track over those years. I also express my deepest gratitude towards my Cosupervisor Professor Dr. Nowshad Amin. He has been a constant source of ideas and technical guidance during the entire time of my research work. Without support from Professor Nowshad, my venture into the world of research would not have been possible. I also wish to express my deepest gratitude towards Professor Dr. A.H.M. Asadul Huq, Chairman, Dept. of Electrical and Electronic Engineering.

This research work would not have been possible without the financial support I got from the Government. I would like to thank ICT Division, Ministry of Posts, Telecommunication and IT, Govt. of Peoples' Republic of Bangladesh, for their fellowship.

My success in this endeavor is largely a result of being lucky enough to meet the right people. I hope I have made their contributions to a success. For direct contribution to the content of this thesis, my gratitude to the Director, Mr. Mahbubul Hoq for his support and valuable suggestions throughout the entire work and allowed me to use the Laboratories at IE, AERE for a greater extended period. I thank Senior Scientific Officer, Khairul Bashar, Rafique Akhond, Md. Rakibul Hasan for fabrication procedure & diffusion furnace operation on commercial silicon wafer at Solar Cell Fabrication Laboratory, Atomic Energy Research Establishment. I thank Senior Scientific Officer, Sardar Masud Rana, who served as great source of advice and inspiration. I thank Senior Scientific Officer, Mr. Anzan-Uz-Zaman for his valuable suggestion in explaining Spectroscopic reflectometer and Nasrul Haque Mia for Dektak operation in VLSI Laboratory AERE.

I thank Project Director, Mr. Shahriar Bashar, BCSIR who allowed me to use characterization tools in the Solar Energy Technology laboratory for a greater extended period.

I am grateful to a number of PhD students who assisted me in several phases of the work. In particular, thanks to Md. Abul Hossion for four point probe, hot probe instrumental set up, several characterizations at AERE, Puvaneswaran Chelvanathan, Naveed Aziz Khan, Kazi Sajedur Rahman who helped me get trained on spin coater and RTP annealing furnace during P5O9 doping stage of my work, Yulisa Binti Mohd Yusoff, Norazlynda Samsudin, Siti Nurlieza Binti Mustafa for chemical etching in the Thin Film Laboratory, Solar Energy Research Institute (SERI).

I am also thankful all lab stuff in particular, thanks to Md. Kamrul Islam, Md. Aminul Islam for their active participation during the entire fabrication of commercial silicon solar cell.

I am thankful to a numbers of labs where I have performed the research work. I am thankful to Solar Cell Fabrication Laboratory, Centre of Excellence for VLSI Technology; Atomic Energy Research Establishment, Material Science Division, Atomic Energy Centre, Dept. of Glass & Ceramic Engineering, Bangladesh University of Engineering & Technology, Dhaka, Bangladesh. I am also thankful to Thin Film Laboratory and Advanced Solar Cell Fabrication Laboratory, Solar Energy Research Institute (SERI), Universiti Kebangsaan Malaysia, Bangi, Selangor 43600, Malaysia. I am also grateful to Centre for Research on Semiconductor Technology.

Finally and most importantly, I would like to thank my parents, Mr. A. K. M. Kaiser Mollah and Ms. Nasima Khanam, have always been a source of encouragement, support and love.

## **Abstract**

The gap between laboratory scale and commercial silicon solar cells is wider many standard processes are not being practiced in transforming to commercialization. The main objective of this work is to investigate the standard as well as simplified fabrication process applicability to commercially available low-cost silicon wafers. Therefore, it is urgently needed to put an intermediate step in between lab-scale fabrication and fully automated commercial facilities or processes. Eventually, smaller fabrication facilities may be benefitted from these comparative studies and get involved in more human resource extensive with commercially available low-cost silicon wafer. Efficiency was achieved to be 5.96% which proves viability of the approach. This study mainly focused on the investigation of effects of standard fabrication processes to commercially available low-cost silicon wafers therefore conversion efficiency was just regarded as the benchmark. However, a series of other characterization found some correlation between processing steps and quality of layers/devices, which can be considered as the contribution of the study. The relatively lower efficiency was probably caused by the complete procedure in a non-cleanroom environment with in-housebuilt low cost instruments, where thorough optimization of the process is needed. Therefore, it is believed that the efficiency can be improved by the use of standard clean room, alternate procedure of edge isolation, improvement of rapid thermal annealing procedure etc. This work thus showed the bridging gap between small scale laboratory solar cells (crystalline silicon based) with the commercial prototypes produced from extensive knowledge in each processing steps.

# **Contents**

| Cover  |           |                                                |       |

|--------|-----------|------------------------------------------------|-------|

| Origir | nality st | atement                                        | i     |

| Ackno  | owledge   | ements                                         | ii    |

| Abstra | act       |                                                | iv    |

| Conte  | ent       |                                                | vi    |

| List o | f Figure  | es                                             | xi    |

| List o | f Tables  | S                                              | XV    |

| Nome   | enclatur  | e                                              | xvii  |

| 1      | Intro     | duction                                        | 1-22  |

|        | 1.1       | Introduction                                   | 1     |

|        | 1.1       | Energy resources and consumption               | 1     |

|        |           | 1.1.1 Fossil fuel                              | 2     |

|        |           | 1.1.2 Nuclear fuel                             | 3     |

|        |           | 1.1.3 Renewable energy                         | 4     |

|        | 1.2       | Photovoltaic (PV) technology: Past and present | 6     |

|        | 1.3       | Problem Statement                              | 7     |

|        | 1.4       | Research Objectives                            | 8     |

|        | 1.5       | Materials for Photovoltaics                    | 8     |

|        | 1.6       | Mono-crystalline silicon technology            | 10    |

|        | 1.7       | Principle of solar cell operation              | 11    |

|        | 1.8       | Efficiency of silicon solar cell               | 12    |

|        | 1.9       | Review of Literature                           | 13    |

|        | 1.10      | Organization of thesis                         | 16    |

|        | 1.11      | References                                     | 18    |

| 2      | Chara     | acterization techniques                        | 23-36 |

|        | 2.1       | Introduction                                   | 23    |

|        | 2.2       | Measurement of thickness                       | 23    |

|   | 2.3   | Optical reflectance                                    | 24    |  |

|---|-------|--------------------------------------------------------|-------|--|

|   |       | 2.3.1 Spectroscopic Reflectometer                      | 24    |  |

|   |       | 2.3.2 Spectral reflectance measurement (SRM)           | 26    |  |

|   | 2.4   | Surface Morphology                                     | 26    |  |

|   |       | 2.4.1 Scanning Electron Microscopy (SEM)               | 24    |  |

|   |       | 2.4.2 2D optical microscopy                            | 27    |  |

|   | 2.5   | Surface roughness measurement by Stylus surface        |       |  |

|   |       | Profiler                                               | 28    |  |

|   | 2.6   | Compositional analysis by energy dispersive            |       |  |

|   |       | x-ray (EDX) spectroscopy                               | 29    |  |

|   | 2.7   | Optical properties: Surface Photo Voltage Spectroscopy | 29    |  |

|   | 2.8   | Electrical properties measurement by four point probe  | 31    |  |

|   | 2.9   | Light-current-voltage (LIV) tester for IV curve        | 32    |  |

|   | 2.10  | Summary                                                | 34    |  |

|   | 2.11  | References                                             | 35    |  |

| 3 | Chara | acterization of wafer                                  | 37-53 |  |

|   | 3.1   | Introduction                                           | 37    |  |

|   | 3.2   | Mono-crystalline silicon substrate                     | 37    |  |

|   | 3.3   | Hot-point probe theory                                 | 39    |  |

|   | 3.4   | Setup for measurement with hot probe                   | 40    |  |

|   | 3.5   | Material type measurement by hot probe                 | 41    |  |

|   | 3.6   | Wafer thickness measurement by dial indicator          |       |  |

|   | 3.7   | Electrical properties measurement by four point probe  |       |  |

|   | 3.8   | Hot probe characteristic curve analysis                | 44    |  |

|   | 3.9   | Thermal effect on carrier concentration                | 45    |  |

|   |       | 3.9.1 Equation for thermally excited charge carrier c  |       |  |

|   |       | oncentration and impurity concentration                | 45    |  |

|   |       | 3.9.2 Results                                          | 46    |  |

|   |       | 3.9.3 Thermally excited charge carrier concentration   |       |  |

|   |       | by using Poisson's equation                            | 47    |  |

|   |       | 3.9.4 Experimental Results                             | 49    |  |

|   | 3.10  | Summary                                                | 51    |  |

|   | 3.11  | References                                             | 52    |  |

| 4 | Prope | erties of | chemically etched silicon wafers                   | 54-6  | 58    |

|---|-------|-----------|----------------------------------------------------|-------|-------|

|   | 4.1   | Introd    | uction                                             | 54    |       |

|   | 4.2   | Neces     | sity for isotropic and anisotropic etching         | 54    |       |

|   | 4.3   | RCA       | cleaning and texturing process                     | 56    |       |

|   | 4.4   | Thick     | ness of textured silicon sample                    | 58    |       |

|   |       | 4.4.1     | Results                                            | 58    |       |

|   | 4.5   | Struct    | ural characterization                              | 58    |       |

|   |       | 4.5.1     | 2D optical imaging                                 | 59    |       |

|   |       | 4.5.2     | Scanning electron microscope imaging               | 59    |       |

|   |       | 4.5.3     | Pyramid height measurement by stylus surface       |       |       |

|   |       |           | Profilometer                                       | 61    |       |

|   |       |           | 4.5.3.1 Results                                    | 62    |       |

|   | 4.6   | Optica    | al Characterization                                | 63    |       |

|   |       | 4.6.1     | Light reflectivity measurement by Spectroscopic    |       |       |

|   |       |           | Reflectometer                                      | 63    |       |

|   |       |           | 4.6.1.1 Results                                    | 63    |       |

|   |       | 4.6.2     | Light reflectivity measurement by Spectral         |       |       |

|   |       |           | Reflectance Measurement                            | 65    |       |

|   |       |           | 4.6.2.1 Results                                    | 66    |       |

|   | 4.7   | Summ      | nary                                               | 67    |       |

|   | 4.8   | Refere    | ences                                              | 68    |       |

| 5 | Fabri | cation a  | and characterization of emitter layer in Silicon w | vafer | 69-96 |

|   | 5.1   | Introd    | uction                                             | 69    |       |

|   | 5.2   | Therm     | nal diffusion process                              | 70    |       |

|   |       | 5.2.1     | Precautions before handling POCl <sub>3</sub>      | 72    |       |

|   |       | 5.2.2     | Condition for POCl <sub>3</sub> diffusion          | 72    |       |

|   |       | 5.2.3     | Temperature dependent sheet resistivity            | 75    |       |

|   |       | 5.2.4     | Operation and process time                         | 75    |       |

|   |       | 5.2.5     | Single step for doping and surface passivation     |       |       |

|   |       |           | and ARC                                            | 77    |       |

|   |       | 5.2.6     | Contamination control                              | 77    |       |

|   |       | 5.2.7     | Challenges for Cl <sub>2</sub> gas removal         | 78    |       |

|   | 5.3   | Spin-c    | on process                                         | 78    |       |

|   |       | 5.3.1     | Precautions before handling P5O9                   | 80    |       |

|   |       | 5.3.2   | Operation and process time                          | 80     |

|---|-------|---------|-----------------------------------------------------|--------|

|   |       |         | 5.3.2.1 Film grown by spin coater                   | 80     |

|   |       |         | 5.3.2.2 Baking                                      | 81     |

|   |       |         | 5.3.2.3 Diffusion by RTP furnace                    | 81     |

|   | 5.4   | Dip co  | pating by P5O9                                      | 83     |

|   | 5.5   | Edge l  | Isolation                                           | 85     |

|   | 5.6   | List of | f samples for diffusion process                     | 84     |

|   | 5.7   | Proper  | rties of emitter layer in silicon wafer             | 85     |

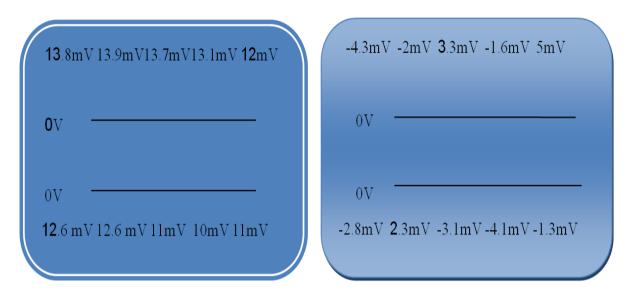

|   |       | 5.7.1   | Polarity measurement by hot probe                   | 85     |

|   |       | 5.7.2   | Measurement of doping uniformity with hot           |        |

|   |       |         | probe                                               | 86     |

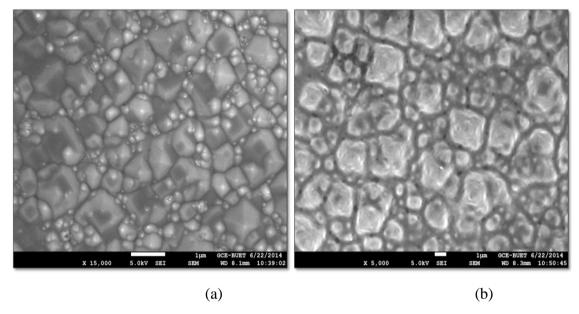

|   |       | 5.7.3   | Surface topography by scanning electron             |        |

|   |       |         | microscope                                          | 87     |

|   |       | 5.7.4   | Energy dispersive x-ray spectroscopy (EDS)          |        |

|   |       |         | analysis                                            | 88     |

|   |       | 5.7.5   | Optical Reflectance                                 | 90     |

|   |       | 5.7.6   | Resistivity by four point probe measurement         | 91     |

|   |       | 5.7.7   | Measurement of thickness                            | 92     |

|   | 5.8   | Summ    | nary                                                | 93     |

|   | 5.9   | Refere  | ences                                               | 95     |

| 6 | Measi | uremen  | t for carrier lifetime and conversion efficiency    | 97-115 |

|   | 6.1   | Introd  | uction                                              | 97     |

|   | 6.2   | Metall  | lization and co-firing                              | 97     |

|   | 6.3   | Minor   | ity carrier diffusion length                        | 98     |

|   | 6.4   | Measu   | rement of minority carrier diffusion length through |        |

|   |       | SPV     |                                                     | 99     |

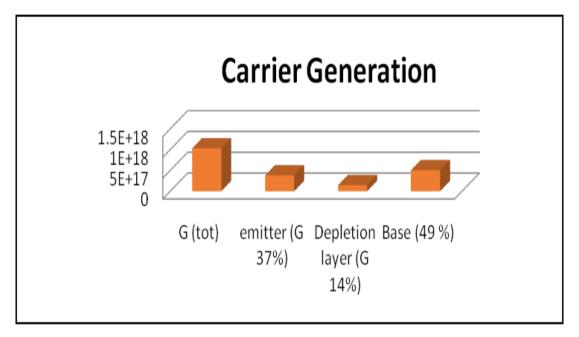

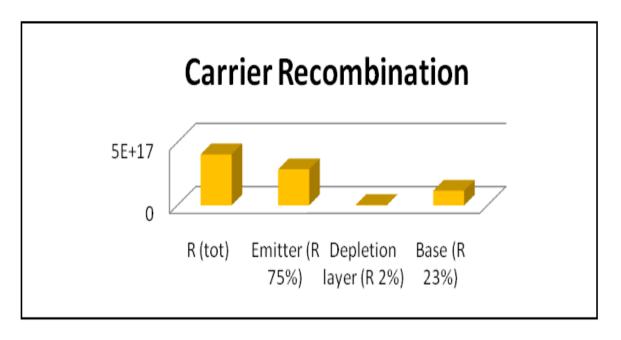

|   | 6.5   | Carrie  | r generation and recombination                      | 99     |

|   | 6.6   | Quant   | itative derivation of carrier generation and        |        |

|   |       | recom   | bination                                            | 101    |

|   | 6.7   | Experi  | imental details                                     | 102    |

|   |       | 6.7.1   | Minority carrier diffusion length                   | 102    |

|   |       | 6.7.2   | Minority carrier lifetime                           | 105    |

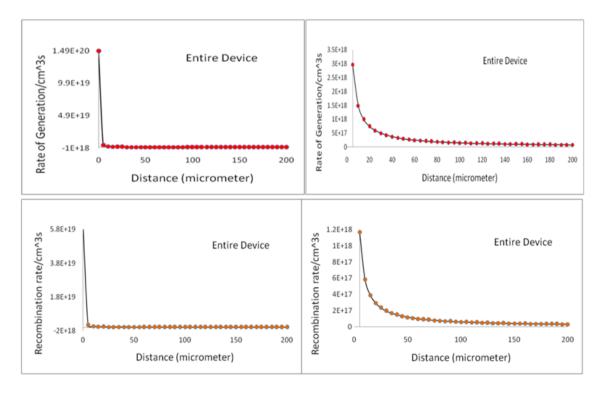

|   |       | 6.7.3   | Carrier generation and recombination                | 105    |

# Dhaka University Institutional Repository

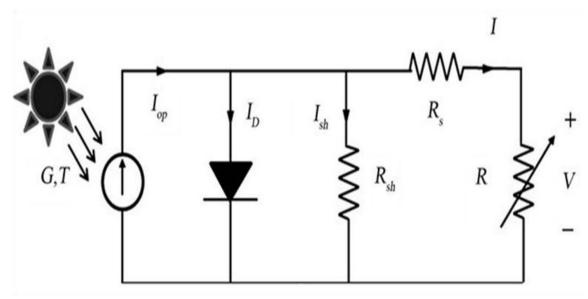

|   | 0.8   | Equivalent circuit for solar cell    | 109 |

|---|-------|--------------------------------------|-----|

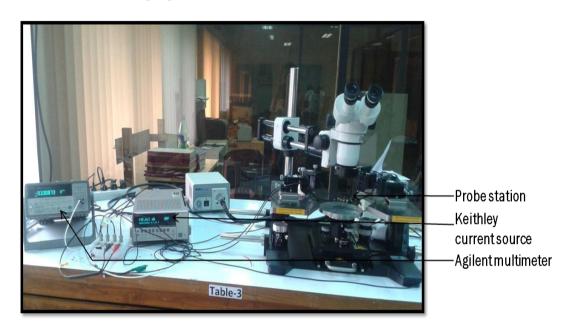

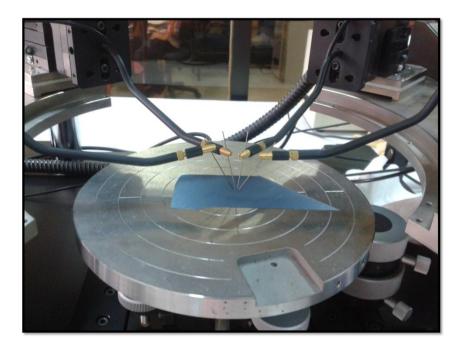

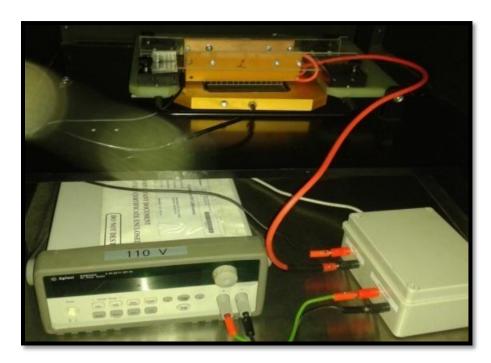

|   | 6.9   | LIV setup for measurement            | 111 |

|   | 6.10  | Measurement of Conversion efficiency | 111 |

|   | 6.11  | Summary                              | 113 |

|   | 6.12  | References                           | 114 |

|   |       |                                      |     |

| 7 | Concl | usion                                | 116 |

|   | 7.1   | Summary                              | 116 |

|   | 7.2   | Future Prospects                     | 119 |

# **List of Figures**

# Chapter I

| Figure 1.1 Global energy consumption at year 2013                            | 1    |

|------------------------------------------------------------------------------|------|

| Figure 1.2 Fossil fuel energy consumption on 1971 (% of total)               | 2    |

| Figure 1.3 Fossil fuel energy consumption on 2013 (% of total)               | 3    |

| Figure 1.4 Alternative and nuclear energy (% of total energy use)            | 4    |

| Figure 1.5 Renewable energy potential in 2009                                | 5    |

| Figure 1.6 Price history of silicon PV cells in \$ per watt                  | 7    |

| Figure 1.7 Bandgap and efficiencies for photovoltaic materials               | 9    |

| Figure 1.8 Working principle of solar cell                                   | 12   |

| Figure 1.9 Telstar communication satellite                                   | 14   |

| Chapter II                                                                   |      |

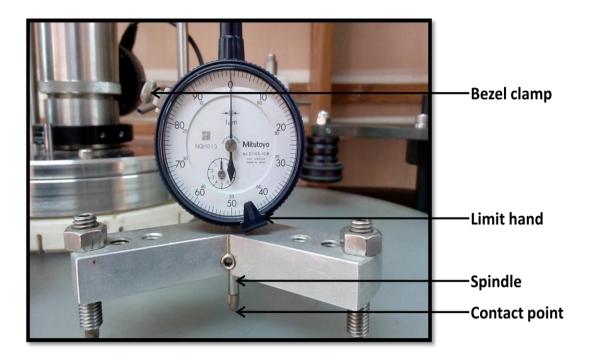

| Figure 2.1 Front view of dial indicator                                      | 24   |

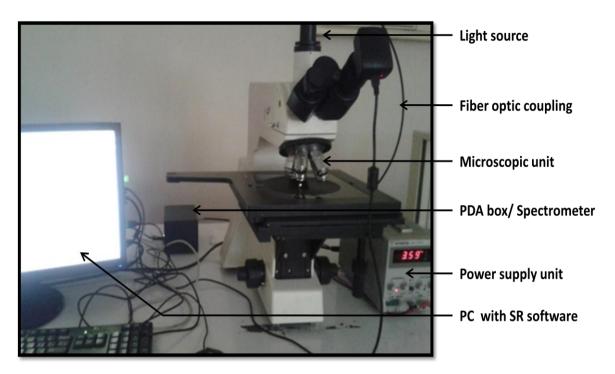

| Figure 2.2 Front view of spectroscopic reflectometer                         | 25   |

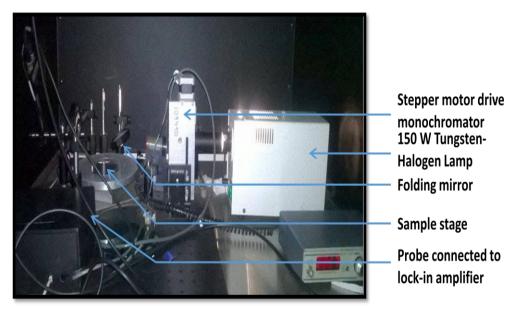

| Figure 2.3 Front view of surface reflectance measurement                     | 26   |

| Figure 2.4 Front view of Scanning electron microscope                        | 27   |

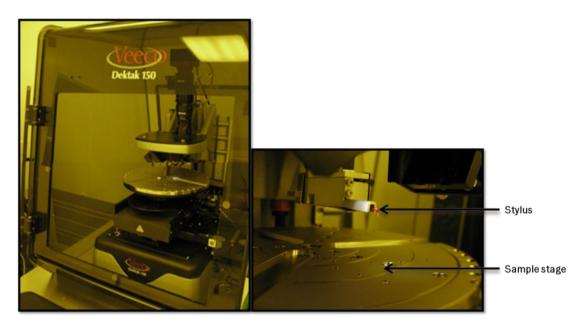

| Figure 2.5 (a) Front view of dektak stylus surface profiler (b))             |      |

| Close view of stylus tip                                                     | 28   |

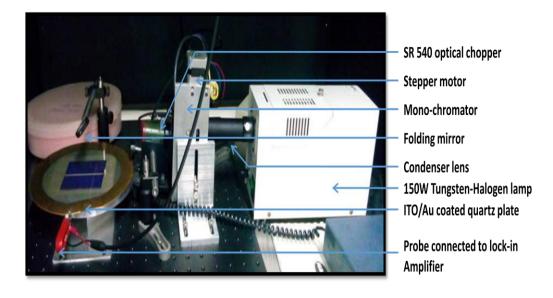

| Figure 2.6 (a) Front view of SPV spectroscopy (b) ) Front view of            |      |

| stanford researc h 510 lock-in amplifier                                     | 30   |

| Figure 2.7 (a) Four point probe (b) ) Close view of four point probe         | 31   |

| Figure 2.8 Front view of LIV efficiency measurement instrument               | 33   |

| Chapter III                                                                  |      |

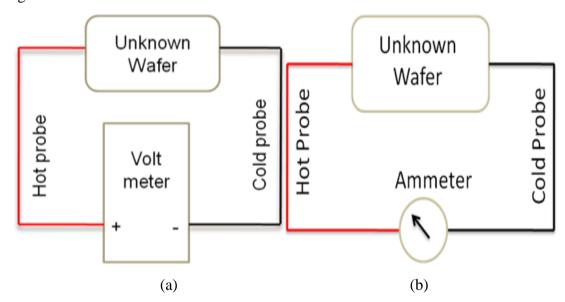

| Figure 3.1 Two alternate block diagram of hot-point probe measurement system | ı 39 |

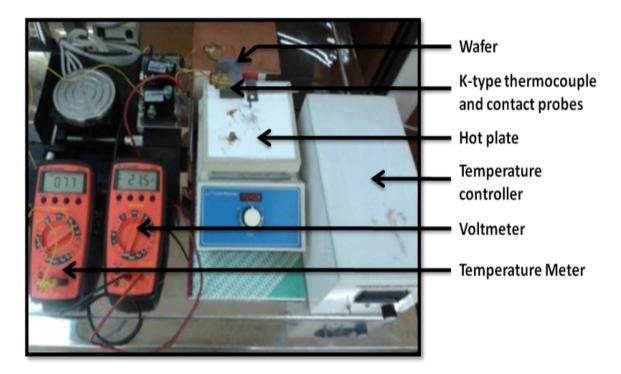

| Figure 3.2 A low cost, in house made hot probe setup                         | 41   |

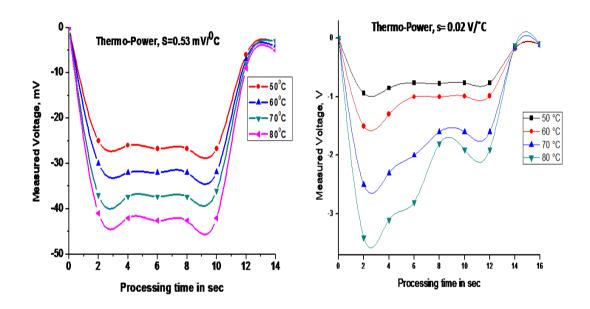

| Figure 3.3 Hot probe characteristic curves for (a) sample-1 and (b) sample-2 | 44   |

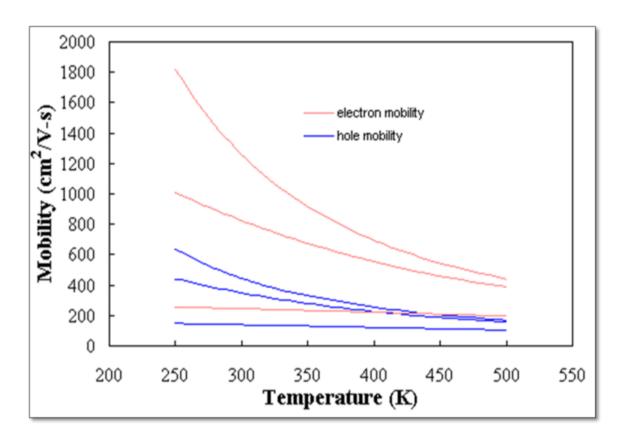

| Figure 3.4 Carrier mobility versus temperature for silicon                   | 47   |

| Chapter IV                                                                                    |         |

|-----------------------------------------------------------------------------------------------|---------|

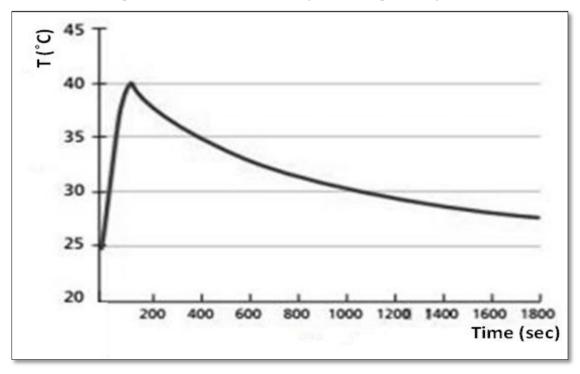

| Figure 4.1 Dissolved NaOH in water, release heat                                              | 56      |

| Figure 4.2 RCA cleaning for silicon sample preparation                                        | 57      |

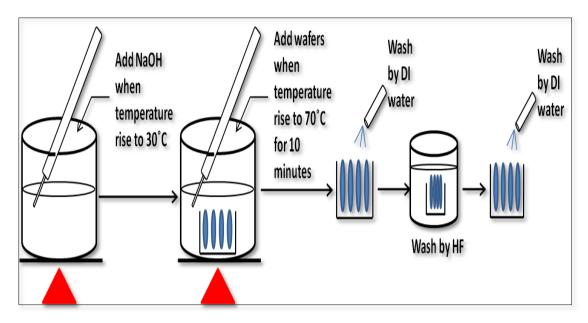

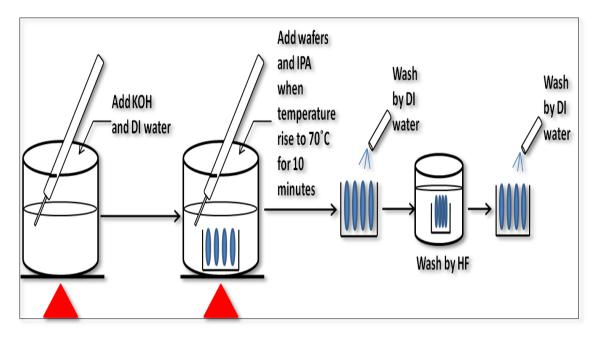

| Figure 4.3 Texturing procedures for silicon sample                                            | 58      |

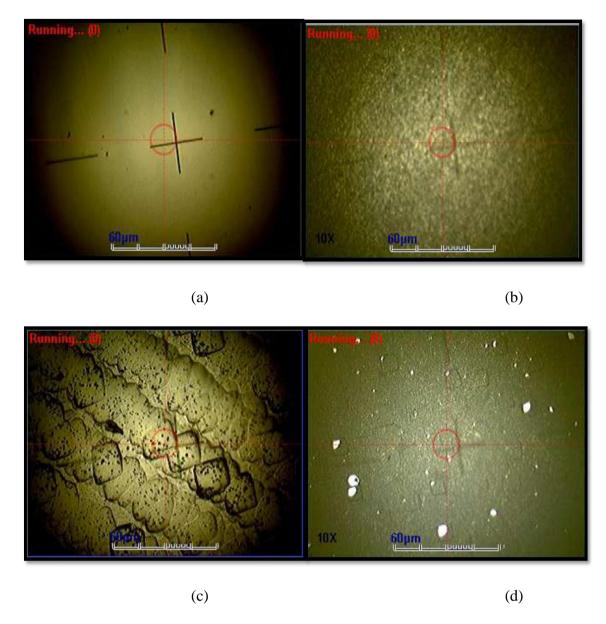

| Figure 4.4 2D optical images with magnification 10x for sample-1 (a) SiCr                     |         |

| Referenc e sample for calibration (b) raw silicon wafer (c) cleaned                           |         |

| silicon wafer (d) textured silicon wafer                                                      | 60      |

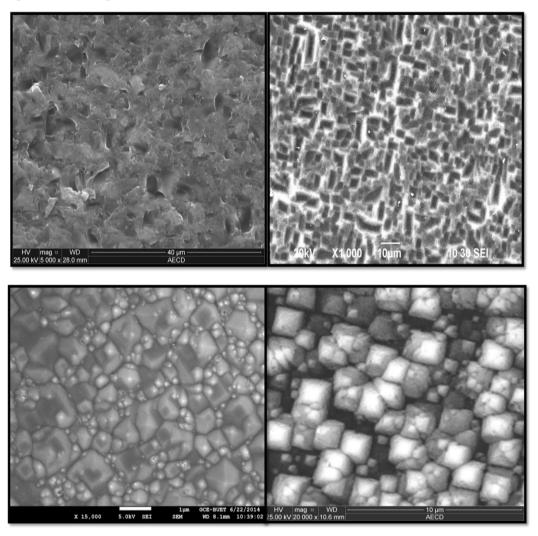

| Figure 4.5 SEM images of silicon sample-1 (a) Raw wafer (b) Saw damage                        |         |

| removed wafer (c) textured silicon wafer (d) textured wafer of silicon sample-2               | 61      |

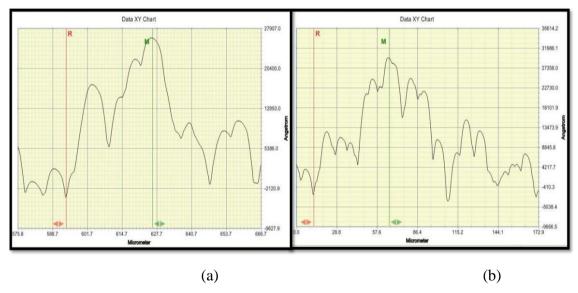

| Figure 4.6 Sample 1 (a) and (b) Surface roughness profile                                     | 62      |

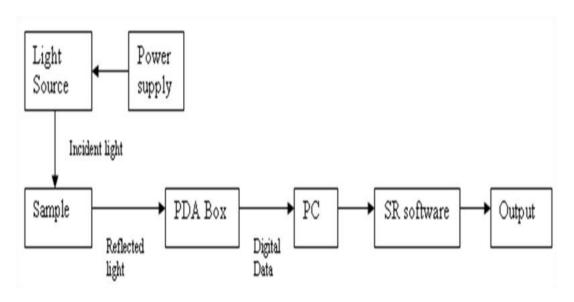

| Figure 4.7 Block diagram of spectroscopic reflectometer                                       | 63      |

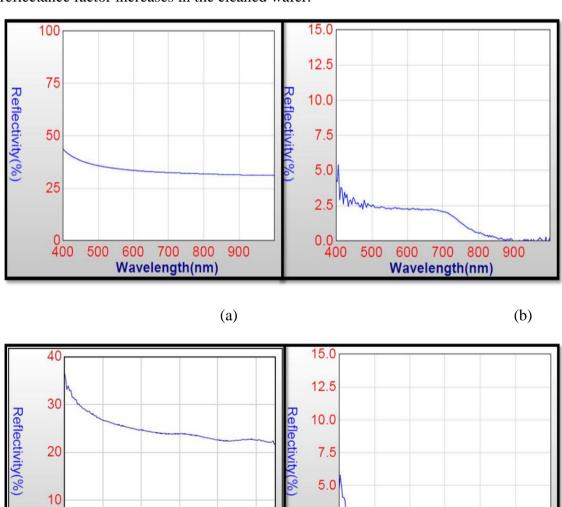

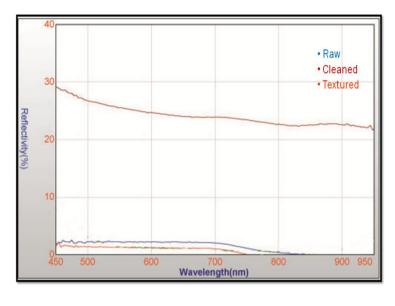

| Figure 4.8 (a) Reflectivity graph of SiCr reference sample for calibra                        | tion.   |

| % Reflectivity  Vs  wavelength  graph  for  silicon  sample-1 (650-800  nm)                   | (b)     |

| %Reflectivity for raw silicon wafer is about 2.4% (c) %Reflectivity for cle                   | aned    |

| silicon wafer is about 24% (d) %Reflectivity for textured silicon wafer is about              | t 1%    |

| that is reduced by multiple reflection from the pyramid growth (e) Comparison                 | n of    |

| %reflectivity for raw, cleaned and textured silicon wafer.                                    | 65      |

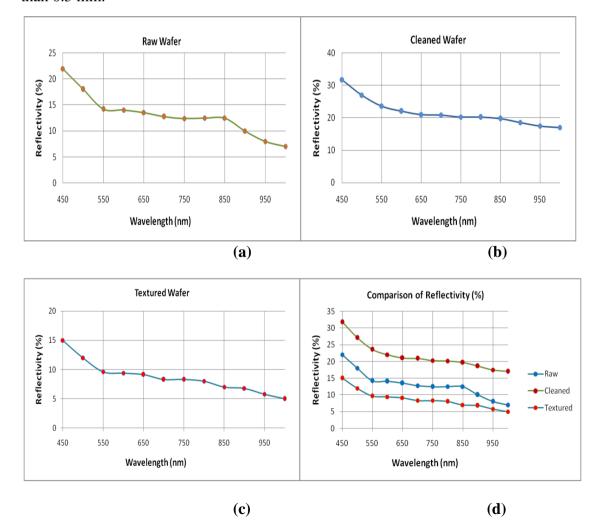

| Figure 4.9 %Reflectivity versus wavelength graph for silicon sample-1 (650-800                | nm)     |

| (a) %Reflectivity for raw silicon wafer is about 13% (b) %Reflectivity for cle                | aned    |

| silicon wafer is about 21% (c) %Reflectivity for textured silicon wafer is about              | t 8%    |

| that was reduced by multiple reflection from the pyramid growth (d) Comparison                | on of   |

| %reflectivity for raw, cleaned and textured silicon wafer.                                    | 67      |

| Chapter V                                                                                     |         |

| Chapter V                                                                                     |         |

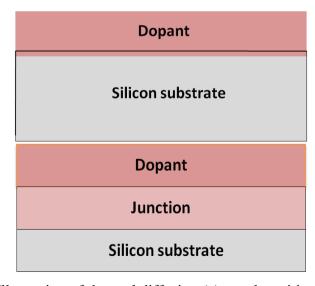

| Figure 5.1 Illustration of thermal diffusion (a) pre-deposition (b) drive-in                  | 70      |

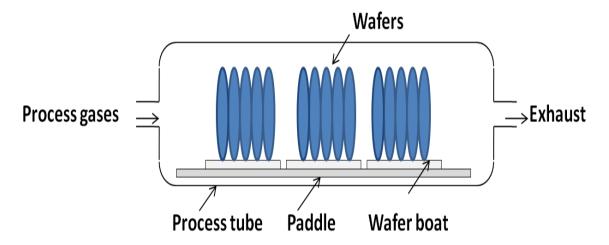

| Figure 5.2 Wafer loading in the horizontal thermal diffusion system                           | 71      |

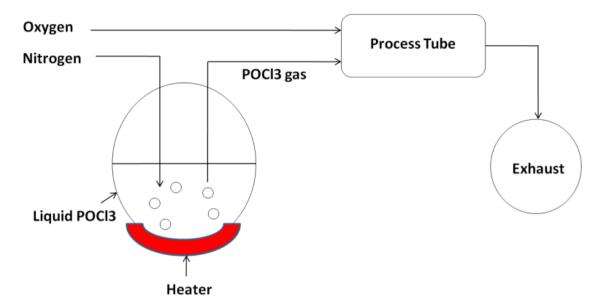

| Figure 5.3 Bubbler system                                                                     | 72      |

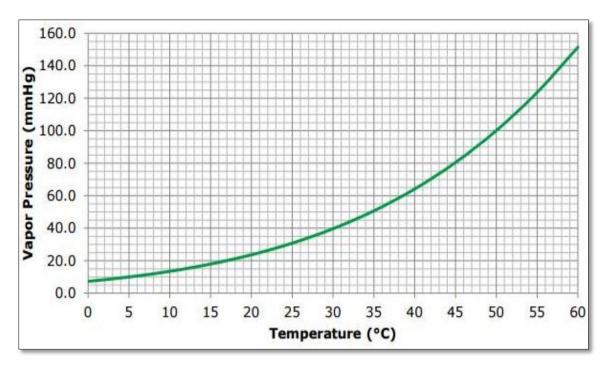

| Figure 5.4 Graph for Bubbler temperature versus POC13 vapor pressure                          | 74      |

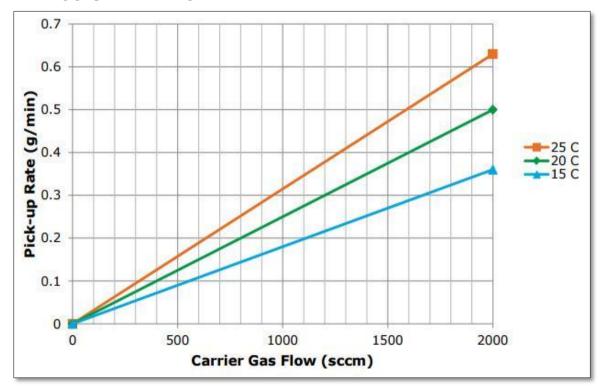

| Figure 5.5 Graph for carrier gas flow versus pickup rate at three different bul               | obler   |

| temperatures                                                                                  | 74      |

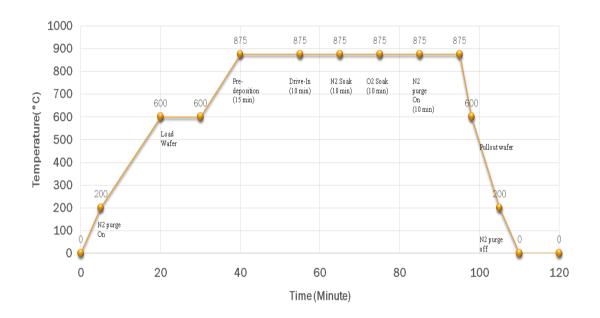

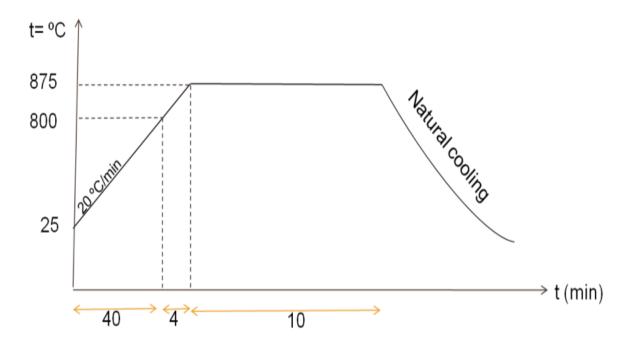

| Figure 5.6 Temperature profile for growth of emitter layer by POCl <sub>3</sub> thermal diffu | sion 76 |

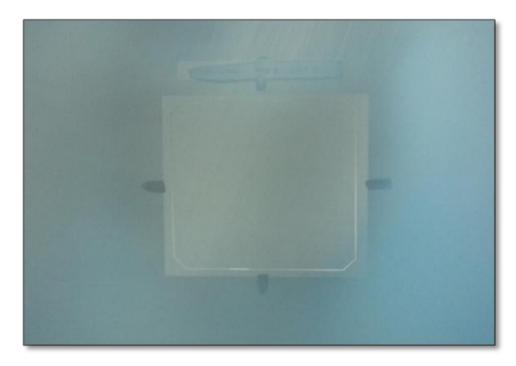

| Figure 5.7 Image of in house doped mono-silicon wafers                                        | 77      |

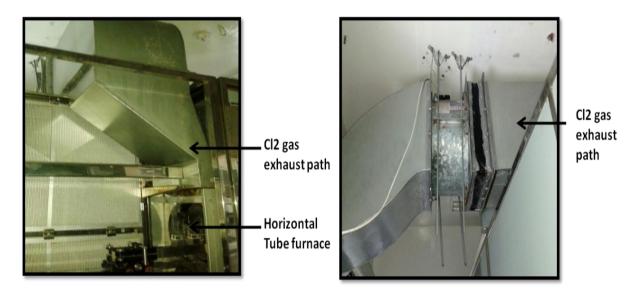

| Figure 5.8 Cl <sub>2</sub> gas exhaust system                                                 | 78      |

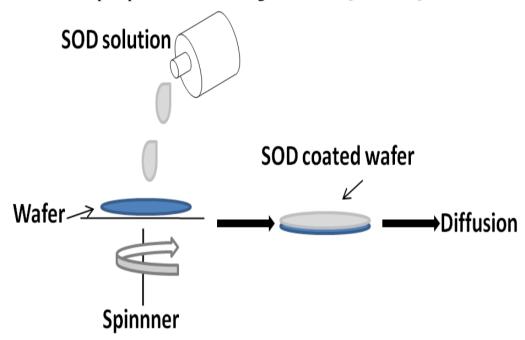

| Figure 5.9 Spin on doping system                                                              | 79      |

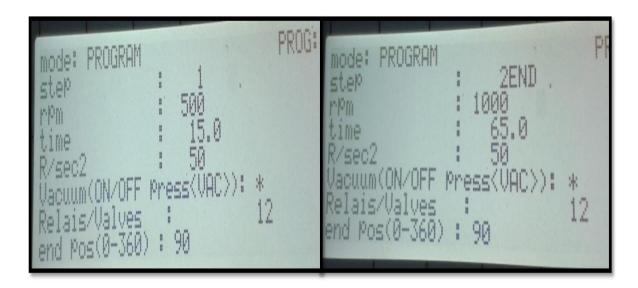

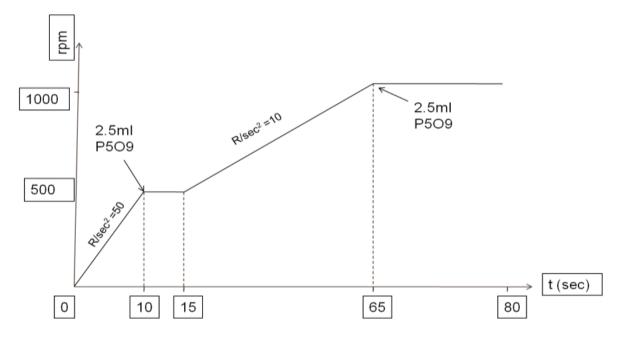

| Figure 5.10 Two step program on SPS Spin 150 spin coater                                | 81      |

|-----------------------------------------------------------------------------------------|---------|

| Figure 5.11 rpm versus time profile                                                     | 81      |

| Figure 5.12 Time versus annealing temperature profile                                   | 82      |

| Figure 5.13 Diffusion Process inside the annealing furnace                              | 83      |

| Figure 5.14 Edge isolation mask screen                                                  | 83      |

| Figure 5.15 Wafer mapping for sample-1 (a) front surface (b) rear surface               | 87      |

| Figure 5.16 Comparison between (a) textured and (b) phosphorus                          |         |

| doped sample-1                                                                          | 88      |

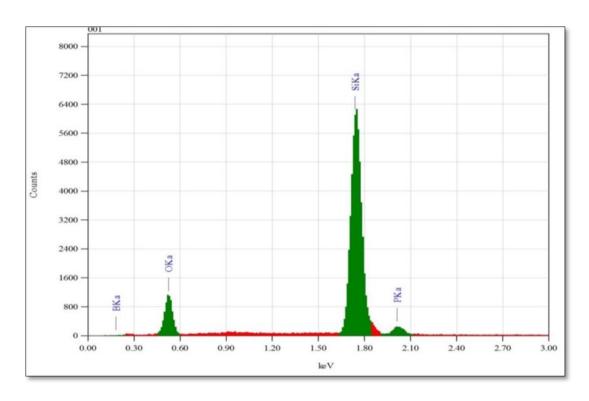

| Figure 5.17 EDS spectrum of doped sample-1                                              | 89      |

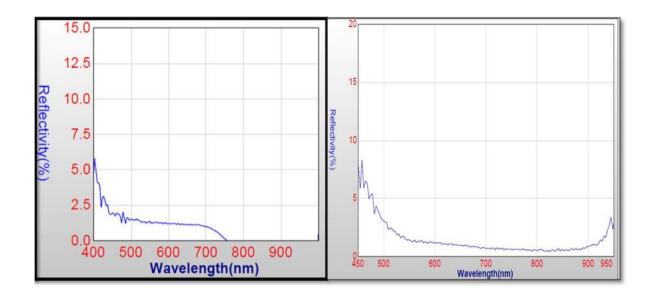

| Figure 5.18 %Reflectivity versus Wavelength graph for sample-1 (a)                      |         |

| Textured silicon sample (b) doped silicon sample                                        | 91      |

| Chapter VI                                                                              |         |

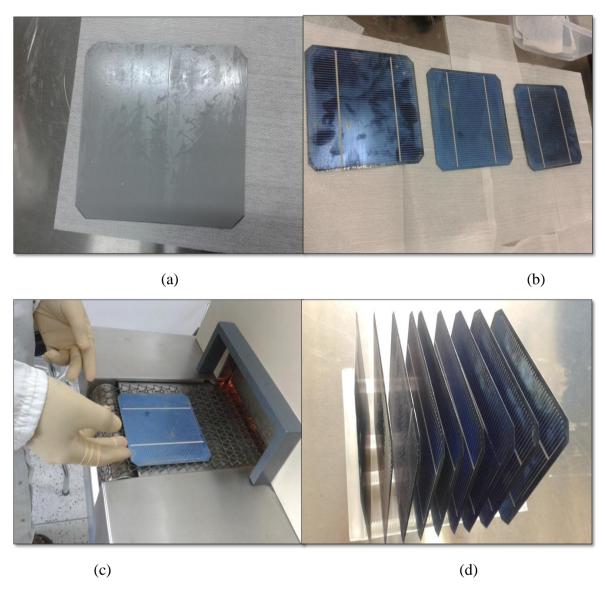

| Figure 6.1 (a) Screen printed rear surface by Al paste (b) Screen printed front s       | surface |

| by Ag paste (c) Co-firing process by belt furnace (d) Fabricated mono-silico            | n solar |

| cell                                                                                    | 98      |

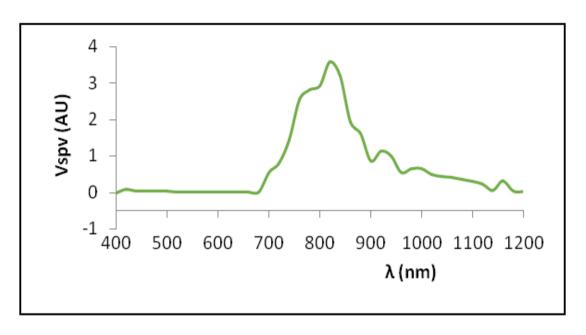

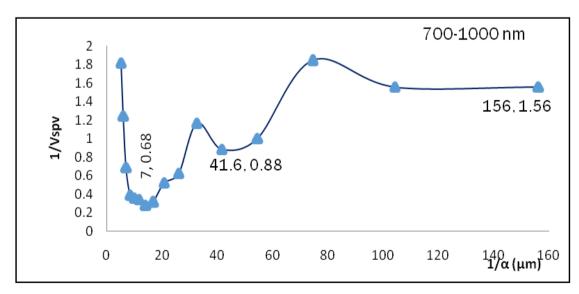

| Figure 6.2 $V_{SPV}$ versus wavelength ( $\lambda$ ) graph: an output from the SPV      |         |

| measurement                                                                             | 103     |

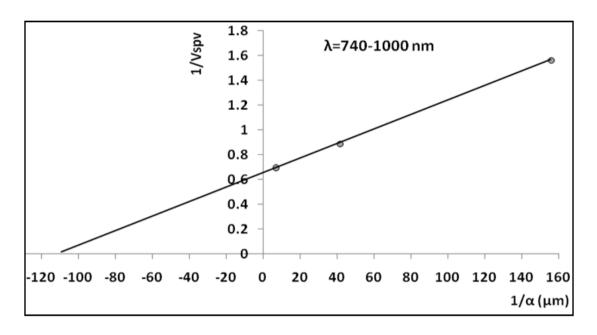

| Figure 6.3 $(\frac{1}{V_{SPV}})$ versus $(\frac{1}{\alpha})$ graph                      | 103     |

| Figure 6.4 The straight line cut at -110 $\mu m$ that gives the value of diffusion leng | th 105  |

| Figure 6.5 Carrier generation for sample-1                                              | 106     |

| Figure 6.6 Carrier recombination for sample-1                                           | 107     |

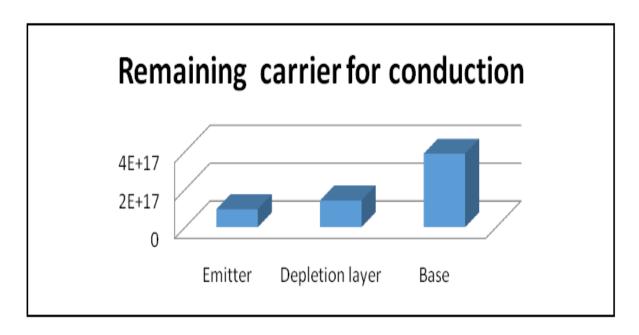

| Figure 6.7 Remaining carrier for sample-1                                               | 108     |

| Figure 6.8 Total carrier generation and recommbination rate for the entire              |         |

| thickness of sample-1 solar cell (left) and rest of the cell ignoring the               |         |

| surface (right)                                                                         | 108     |

| Figure 6.9 A diode circuit model describing a PV cell connected to a source             |         |

| meter for IV testing                                                                    | 109     |

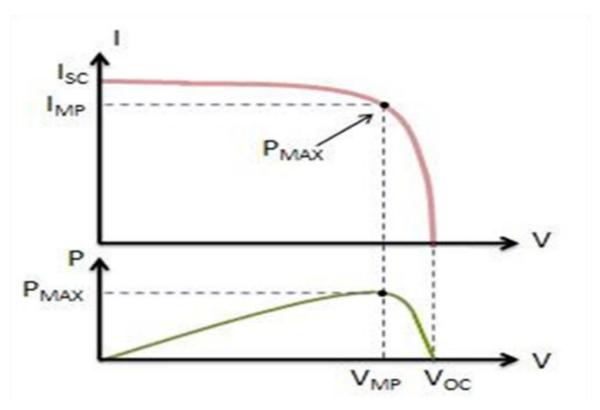

| Figure 6.10 IV curve for a silicon PV cell                                              | 110     |

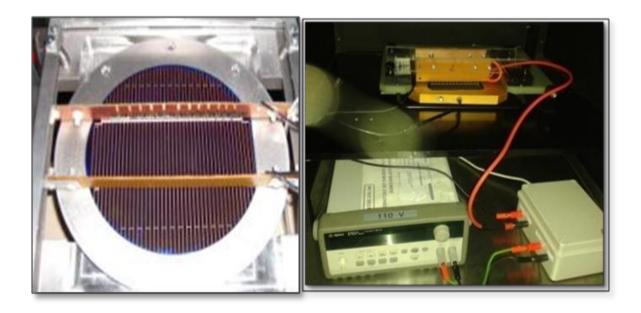

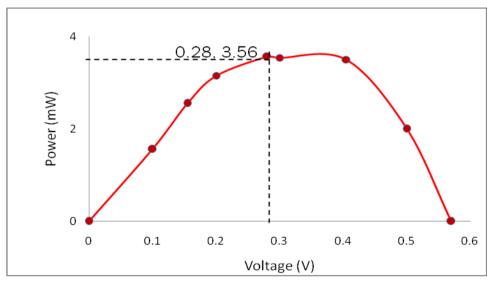

| Figure 6.11 (a) Custom designed probes (b) Programmable                                 |         |

| current-voltage measurement power supply with LAB VIEW based                            |         |

| interface                                                                               | 111     |

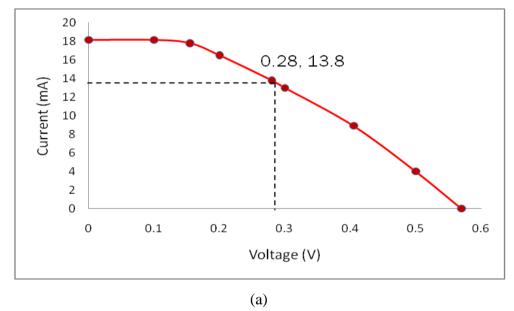

| Figure 6.12 (a) I-V curve (b) P versus V curve for mono-silicon solar cell              |         |

| $(125 \times 125 \text{ mm}^2)$                                                         | 112     |

# Appendix I

| Figure App 1: Front side view of De-ionized water plant                          | 122   |

|----------------------------------------------------------------------------------|-------|

| Figure App 2: (a) Front side view of laser cutter (b) Silicon wafer under        |       |

| the laser cutter                                                                 | 123   |

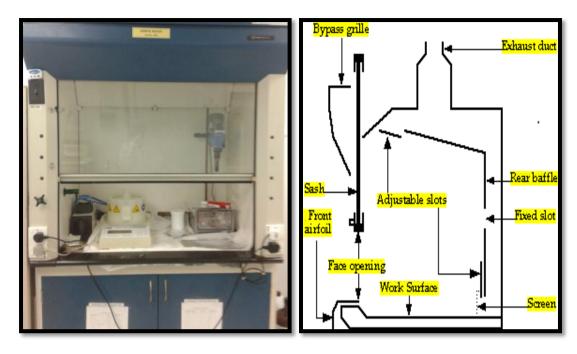

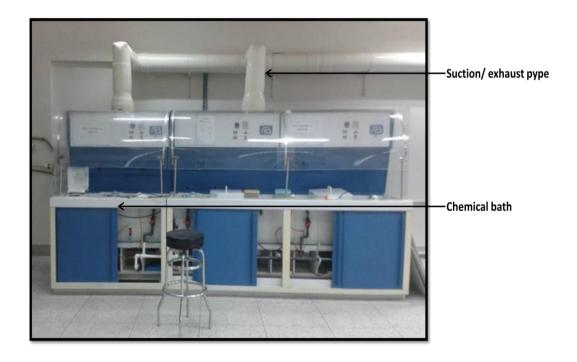

| Figure App 3: (a) Front side view of fume hood (b) Basic parts of fume hood      | 124   |

| Figure App 4: Front side view of sample cleaning bath                            | 124   |

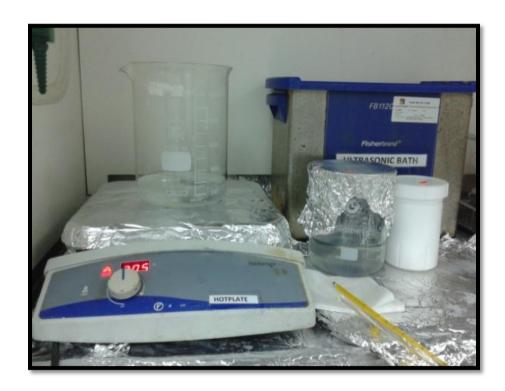

| Figure App 5: Front side view of hot plate                                       | 125   |

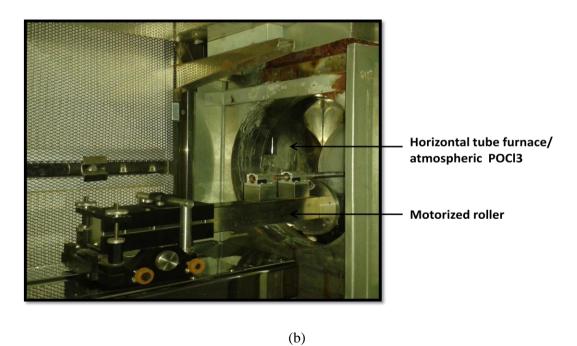

| Figure App 6: (a) Front side view of diffusion furnace (b) Motorized roller carr | y the |

| wafer inside the horizontal diffusion furnace                                    | 126   |

| Figure App 7: Front side view of spin coater                                     | 127   |

| Figure App 8: Front side view of annealing furnace                               | 128   |

| Figure App 9: Screen printer                                                     | 129   |

| Figure App 10: Front side view of RTA belt furnace                               | 130   |

# **List of Tables**

| Cnapter 1                                                                         |                         |

|-----------------------------------------------------------------------------------|-------------------------|

| Table 1.1 Properties of silicon                                                   | 11                      |

| Table 1.2 Highest confirmed terrestrial solar cell efficiency measured under A    | M1.5                    |

| spectrum                                                                          | 13                      |

| Table 1.3 Major process steps, parameters and the monitoring techniques used in   | solar                   |

| cell fabrication                                                                  | 16                      |

| Chapter III                                                                       |                         |

| Table 3.1 Sample name, Thicknesses and the supplier name                          | 38                      |

| Table 3.2 Measurement of wafer type using indigenously made hot probe system      | 42                      |

| Table 3.3 Measurement of wafer thickness using dial indicator                     | 42                      |

| Table 3.4 Resistivity measurement using four probe techniques                     | 43                      |

| Table 3.5 Thermo-power measurement using hot probe characteristic curve           | 45                      |

| Table 3.6 Acceptor concentration at room temperature with respect to ph           | ysical                  |

| resistivity                                                                       | 47                      |

| Table 3.7 Temperature dependent hole mobility $(\mu_p)$ , impurity concentration  | on $(N_A)$ ,            |

| function of heating temperature ® and thermally excited charge carrier density (A | ∆ <i>p</i> ) 48         |

| Table 3.8 Temperature dependent steady state voltage, hole diffusion coefficient  | $\operatorname{t}(D_p)$ |

| and thermally excited charge carrier $(Q)$                                        | 50                      |

| Table 3.9 Comparison between theoretical and experimental values of the           | mally                   |

| excited charge carrier concentration                                              | 50                      |

| Chapter IV                                                                        |                         |

| Table 4.1: Thickness comparison table for raw and textured mono silicon sample    | 59                      |

| Table 4.2: Measurement of pyramid height using stylus surface profilometer        | 62                      |

| Chapter V                                                                         |                         |

| Table 5.1 Various gas flow rate for APCVD thermal diffusion                       | 73                      |

| Table 5.2 Temperature dependent solid solubility of phosphorus and the            |                         |

| sheet resistivity for silicon sample                                              | 75                      |

| Table 5.3 List of samples: n-type emitter formation on p type silicon substrate   | using                   |

| APCVD thermal diffusion, spin on doping and dip coating by SOD solution           | 85                      |

| Table 5.4 Polarity measurement by using hot probe                                 | 86                      |

| Table 5.5 Doping uniformity measurement by hot probe                              | 87                      |

| Table 5.6 Compositional analysis using EDS                                    | 90  |

|-------------------------------------------------------------------------------|-----|

| Table 5.7 Measurement of sheet resistivity for doped sample using four        |     |

| point probe                                                                   | 92  |

| Table 5.8 SiO <sub>2</sub> ARC film thickness measurement using spectroscopic |     |

| reflectometer                                                                 | 93  |

| Chapter VI                                                                    |     |

| Table 6.1 Carrier generation and recombination for emitter, depletion and     |     |

| base layer                                                                    | 100 |

| Table 6.2 Penetration depth and $1/V_{SPV}$ with respect to wavelength        | 104 |

| Table 6.3 Carrier generation for emitter, depletion and base layer            | 106 |

| Table 6.4 Carrier recombination for emitter, depletion and base layer         | 106 |

| Table 6.5 Remaining carrier for emitter, depletion and base layer             | 107 |

| Table 6.6 Data for reference cell                                             | 112 |

| Table 6.7 Findings from in house fabricated mono-silicon solar cell           |     |

| $(125 \times 125 \text{ mm}^2)$                                               | 113 |

# Nomenclature

| APCVD- Atmospheric | Pressure | Chemical | Vapor I | Deposition |

|--------------------|----------|----------|---------|------------|

|--------------------|----------|----------|---------|------------|

ASH- Average Step Height

CVD- Chemical Vapor Deposition

DI- De-ionized

EDX- Energy dispersive x-ray spectroscopy

FE-SEM- Field Emission Scanning Electron Microscopes

HF- Hydro fluoric acid

IC- Integrated circuit

IPA- Isopropyl alcohol (Iso 2-propanol)

LIV- Light-current-voltage

PV- Photo voltaic

RCA- Radio Corporation America

SEM- Scanning electron microscopy

SOD-Spin on dopant

SPV- Surface photovoltage

SR- Spectroscopic Reflectometer

SRM- Spectral reflectance measurement

# **Chapter I**

# Introduction

### 1.1 Energy resources and consumption

The estimated maximum capacity for energy production given to all available resources on earth is called the world energy resources. The world's energy resources are divided into fossil fuel, nuclear energy and renewable energy [1]. Energy consumption refers to the amount of energy consumed in a process or by an organization or society. World energy consumption refers to the total energy used by all human civilization that is measured per year. The measurement involves all energy collect from every energy source and applied towards every single industrial and technological sector across every country [2].

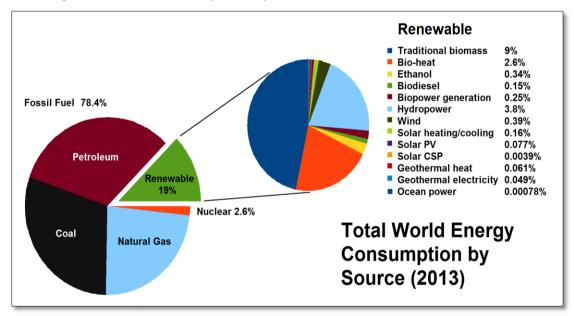

Figure 1.1 Global energy consumption at year 2013 [3]

Several institutions are involved to record and publish the energy data periodically. Some of them are U.S. International Energy Agency (IEA), the Energy Information Administration (EIA), the European Environment Agency etc [1].

#### 1.1.1 Fossil fuel

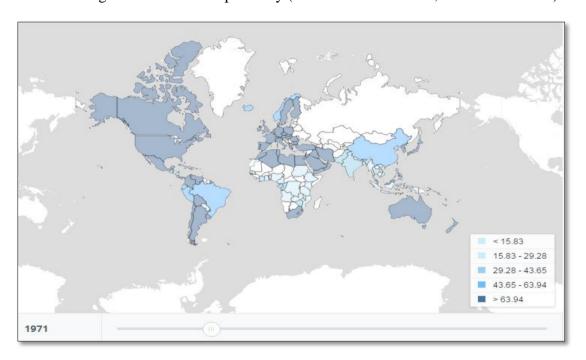

The dominant energy resource from the early years is fossil fuel. The fossil fuel was supplying 86% of the world's energy at 2006 that is reduced with increasing years (source: US Energy Information Administration). Coal is the most burned and fastest growing fossil fuel because of its large reserves that make it popular to meet the energy demand of the global community. International Energy Agency said that the reserves of coal are 909 billion tones which could sustain the current production rate for 155 years. But at a 5% growth per annum the reserve would be reduced to 45 years or until 2051. The scenario of fossil fuel energy consumption in 1971 and 2013 is shown in figure 1.2 and 1.3 respectively (Source: IEA Statistics, OECD/IEA 2014).

Figure 1.2 Fossil fuel energy consumption on 1971 (% of total) [4]

Figure 1.3 Fossil fuel energy consumption on 2013 (% of total) [5]

China is the example of coal fuel user in their industry that causes its polluted cities [6]. Current oil consumption rate is 31.1 billion barrels (or 85-mbd). The peak oil production could be reached in the near future that will cause the severe oil price increases. According to peak oil theory, increasing production will lead to a more rapid collapse of production in the future, while decreasing production will lead to a slower decrease. OPEC had announced to decrease the production of oil by 2.2 mbd at the beginning of 1st January, 2009. The use of natural gas was 131% at 2009 compared to year 2000. North America shared 27% natural gas compared to other countries in 2010. The natural gas comes from European Union, North America, Latin America, Russia, Middle East, Asia, Africa etc [1].

#### 1.1.2 Nuclear fuel

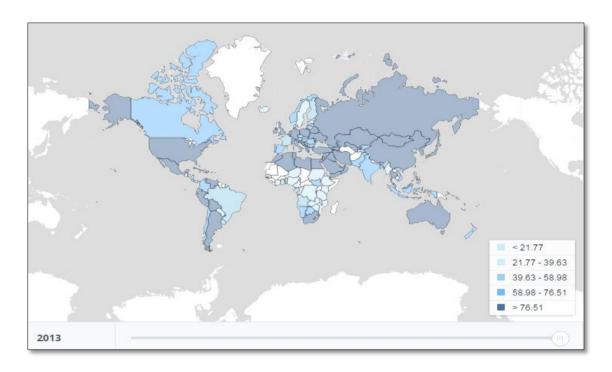

Due to a number of nuclear accidents the energy supply from nuclear fuel has restricted the growth at the end of last century. The world had 444 grid-electric nuclear power reactors with 62 others under construction in 2016. The commercial nuclear energy began in the mid 1950s. No new nuclear power plant was connected to the grid in 2008. But two were connected in 2009. The annual generation has been slight downward since 2007. According to IEA/OECD, Nuclear power met 11.7% of the world's electricity demand in 2011. The scenario of nuclear fuel energy

■ < 5.68 ■ 5.68 - 15.60 ■ 15.60 - 28.52 ■ 28.52 - 39.43 ■ > 39.43

consumption in 2013 is shown in figure 1.4 (Source: IEA Statistics, OECD/IEA 2014).

Figure 1.4 Alternative and nuclear energy (% of total energy use)[7]

Alternative energy production through hydrogen fusion has been started since 1950s. It generates large quantities of heat from the nuclei of hydrogen or helium isotopes. The heat can be used to generate electricity. Fusion is theoretically able to supply vast quantities of energy, with relatively little pollution. United States and the European Union, along with other countries are supporting fusion research [1].

#### 1.1.3 Renewable energy

Day by day the world energy consumption is rising with the growth and development of the civilization. The primary solution of this increasing demand of using conventional energy source such as fossil fuel, nuclear power plant etc. it is now force to look into other renewable energy sources. Most of earth's available energy resources are renewable resources such as solar, wind, wave, tidal power etc.

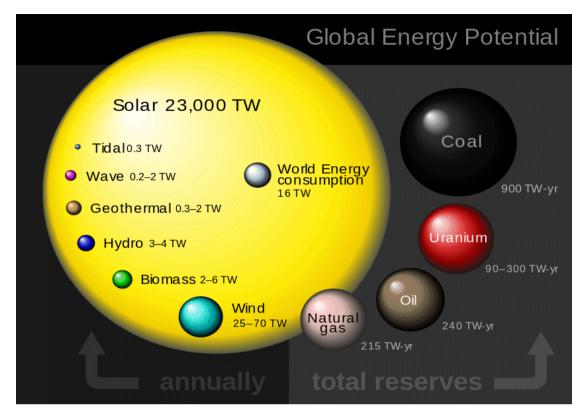

Figure 1.5 Renewable energy potential in 2009 [8]

Figure 1.5 clears that the renewable energy sources are larger than the fossil fuels. Theoretically they can supply the world's energy needs. The solar power that falls on the planet's surface is not possible to capture. Capturing less than 0.02% would be enough to meet the current energy needs. The annual average growth of solar generation was about 35% over the past few years. Japan, Europe, China, U.S. and India are the leading growing investors in solar energy. The drawback is that the current solar generation does not produce electricity at night in high northern and southern latitude countries. The energy demand is highest in winter while availability of solar energy is lowest. During these months the energy lacking could be overcome by buying power from countries closer to the equator. Alsothe technological developments such as the development of inexpensive energy storage can solve the energy crisis.

The estimated range of available wind energy is 300-870 TW (2005) [9]. Using the lower estimate, just 5% of the available wind energy would supply the current worldwide energy needs. The open oceans cover 71% of the planet and wind tends to blow more strongly there because of fewer obstructions.

The tidal forces created by the Moon and the Sun, and the Earth's relative rotation with respect to Moon and Sun. These tidal forces cause tidal fluctuations. Tidal fluctuations result in dissipation at an average rate of about 3.7 TW. At the end of 2005, 0.3 GW of electricity was produced by tidal force. Waves are derived from wind, which is in turn derived from solar energy, and at each conversion there is a drop of about two orders of magnitude in available energy [1].

### 1.2 Photovoltaic (PV) technology: Past and present

The development of photovoltaic began in 1839 when French physicist Edmond Becquerel discovered an increment in current of an electrolyte cell when exposed to light [10]. Nature published the effect of light on selenium during the passage of an electric current in 1873 that was described by British Engineer Willoughby Smith. An American inventor Charles Fritts first implemented the PV device of around 1% efficient in 1883. He had built up a junction by using selenium and thin layer of gold. Russian physicist AleksandrStoletov discovered the law of proportionality between the intensity of light and the corresponding photo induced current. He built the first solar cell based on the outer photoelectric effect and estimated the response time of the photoelectric current in 1888. Note that the outer photoelectric effect discovered by German physicist Heinrich RudlofHertzin in 1887. The Nobel laureate German born theoretical physicist Albert Einstein proposed a new quantum theory of light and explained the photoelectric effect in 1905. The p-n junction in CuO and silver sulphide photocells was described by Ukraine born Soviet experimental physicistVadimEvgenievichLashkaryov in 1941. An American Engineer Russell ShoemakerOhl hadpatented the Light sensitive device in 1946. He was a renowned

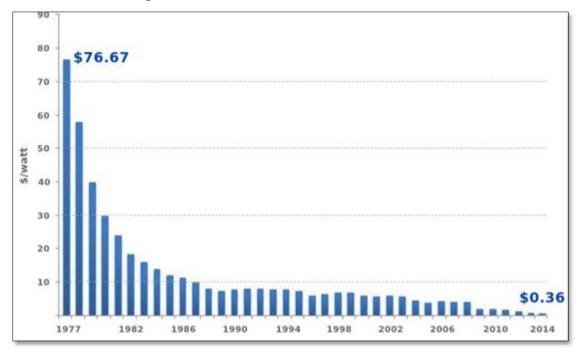

semiconductor researcher prior to the invention of the transistor[11]. In 1954 Bell laboratories scientist Gerald Pearson, Daryl Chapin and Calvin Fuller fabricated the first solar cell using silicon [12]. As the cost of commercial solar cell was as high as 300USD per watt it was not possible for mass production however it can be useful for powering satellites proposed by the mathematician from NewyorkGordon Raisbeck one of Daryl Chapin's colleague in 1955 [13]. Despite the initial concern of photovoltaic's future research continues and cost reduces to 100USD per watt by the year 1970 which was mainly used for powering satellites [14]. At present the

production cost reduces to <1 USD per watt peak for solar modules (≥ 125W) made of multi crystalline silicon [15]. Thus the number of terrestrial solar power unit's increases dramatically in various field of necessity of signaling, communication and remote sensing even powering the water pumps in agricultural fields. Now a days 99% of the terrestrial photovoltaic solar cells are made of silicon [15].

Figure 1.6 Price history of silicon PV cells in \$ per watt [16]

### 1.3 Problem Statement

Since the inception of silicon based solar cells in 1954 by Bell lab researchers with a mere 6% conversion efficiency, the silicon wafer based cells experienced utmost achievement in terms of efficiency to its theoretical limit of around 25%, but still there are possibilities to achieve further improvement in efficiency to the Schokley Quissier limit. However, in terms of commercialization, cost is the most important issue to make it more popular as the competitors like CdTe thin film solar cells are quite comparable with silicon technologies. Therefore, there is a need to have cost reduction in silicon wafers, which is already achieved by thinning technologies as most common are now 180um, whereas initial wafers were over 500um. For mass production, cast silicon technologies are becoming fruitful to get us cheaper monocrystalline silicon wafers. As many companies are developing cheaper silicon wafers and in case of any new comer in silicon wafer manufacturing, standard silicon solar cell processing may not be applicable. Moreover, there is a need for cheaper wafer

with simpler solar cell processing technology to be adopted to make silicon to hold the mainstream of solar cells in use for years to come. However, this sort of combination of raw materials and process should be investigated as most of the research groups are still focusing on higher effficiency issue, making tandem with newer materials like perovskite etc. We need to have more investigation on the characteristics for solar cells fabricated by the combination of cheaper raw materials and simpler process to get us the ultimate benefit from silicon technologies. Therefore, this study will mainly focus on the investigation related to characterization of silicon solar cells fabricated by commercially available low cost silicon wafer by simpler process.

### 1.4 Research Objectives

The main objective is to find out the correlation between the raw materials such as silicon wafer and the process options such as standard fabrication process for silicon monocrystalline solar cells. More precisely, It is to find out what could be the various characteristics such as optical, structural and electrical characteristics of the low-cost commercially available thinner silicon wafers in case processed by simplied process of fabrication in a pilot experimental facility. Therefore, this study embarks on the following specific objectives as shown below:

- 1. To investigate a simplified solar cell fabrication process for commercially available thinner mono crystalline silicon wafer to improve overall cost-efficiency.

- 2. To Explore the standard processes of Emitter Formation, Surface Passivation and Enhanced Light Trapping in case of Thinner silicon wafers.

- To Examine the properties, such as optical, structural and electrical, of the processed wafers by low-cost characterization tools and techniques for process optimization and cost-efficiency.

#### 1.5 Materials for Photovoltaics

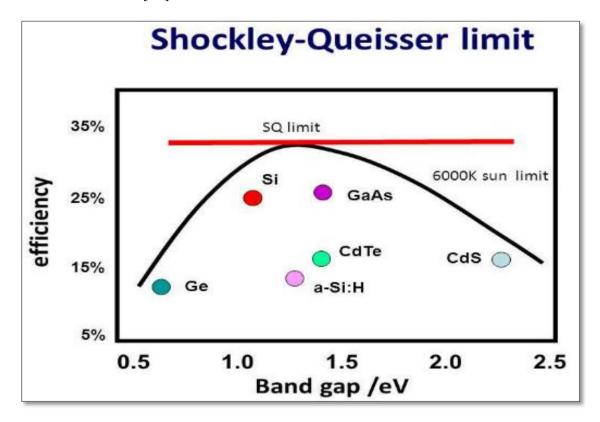

Since only photons with energies above the band gap of a semiconductor are absorbed, the band gap of the material used for a photovoltaic device must be engineered in order to produce the maximum power for a given illumination, given that the solar spectrum as a function of photon energy under one sun condition [18, 19]. Semiconductors with larger band gaps produce higher photovoltages, but absorb and convert fewer of the incident photons, resulting in lower currents. Semiconductors with smaller band gaps absorb most of the solar radiation, but convert most of the energy to heat. A balanced condition for the solar cell with the best efficiency is to use material with band gap near the peak of the solar spectrum, between 1 and 2 eV[20].

Figure 1.7Bandgap and efficiencies for photovoltaic materials[21]

Compound semiconductors GaAs, GaInP, InP, CdTe, and CIS (copper indium diselenide), and indirect band gap materials, like silicon, are used in the fabrication of solar cells. Both amorphous and crystalline (polycrystalline and monocrystalline) silicon are used in the manufacture of photovoltaic devices. However, amorphous silicon suffers from the Staebler-Wronski effect [22], in which dangling bonds are created under illumination, causing the efficiency to degrade. Research communities turn then to crystalline silicon technology, which is capable of providing efficiencies greater than 20% [23]. Material bandgap and related efficiencies is shown in figure 1.7 (Source: DOE, Lewis Group at Caltech).

### 1.6 Mono-crystalline silicon technology

One of the most promising technologies for reduced cost photovoltaic technology involves the reduced thickness mono-crystalline silicon wafer or substrate. The efficiencies of mono-crystalline silicon solar cells have much higher efficiencies than thin-film polycrystalline solar cells. Although production costs are significantly lower for thin film polycrystalline solar cells than the mono-crystalline silicon cells. In 2014 the conversion efficiency of mono-crystalline silicon solar cell reached to 25.6% at research level. Panasonic HIT® solar cells achieved that efficiency with cell area 143.7 cm². The previous record was 24.7% with cell area 100 cm² in 2013 [24].

Generally silicon wafers produce from Czochralski (CZ) process. Most of the PV industries today use the mono-crystalline silicon wafers. Because the monocrystalline silicon wafers have lower defects compared to other wafers. The solar cells produce from this type of wafer has maximized the power density in the PV module and to reduce the cost per unit energy. The wafers are classified in accordance with their crystal orientation, doping type, resistivity, thickness, concentration of oxygen and carbon etc. Today's commercial wafers are of pseudo square shaped (cylinders are shaped as squares with rounded off corners) geometry. Crystal orientation has strong influence on the optical and electrical performance on solar cells. The etching rate of mono-crystalline <100> crystal orientation is higher than the <111>which helps for early growth of pyramids. The wafer size and thickness depends on the ability to handle during cell processing. To reduce the material cost, the wafers are cut into 120-200 µm thickness with multi-wire sawing. Thinner wafer reduce the material consumption may require requires an automated handling process fabrication. Decrease the wafer thickness means increases the possibilities of breaking wafers. Most of industrial solar cells are based on boron doped p-type wafers and n-type diffused emitter. N-type wafer price is still now much higher than p-type. N-type wafer shows large minority carrier diffusion length and carrier lifetime than the p-type wafer [25].

Table 1.1Properties of silicon [26, 27]

| Property                 |                                         | Value                                                                                                         |  |

|--------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------|--|

| Basic parameter at 300 K | Crystal structure                       | Face centered diamond-<br>cubic                                                                               |  |

|                          | Number of atoms in per cm <sup>3</sup>  | 5 x 10 <sup>22</sup> cm <sup>-3</sup>                                                                         |  |

|                          | Density (p)                             | 2.328 gcm <sup>-3</sup>                                                                                       |  |

|                          | Dielectric constant                     | 11.7                                                                                                          |  |

|                          | Lattice Constant                        | 5.431 Å                                                                                                       |  |

| Band structure and       | Energy Bandgap (EG)                     | 1.12 eV (at 300 K)                                                                                            |  |

| carrier concentration    | Intrinsic Carrier<br>Concentration (ni) | 1 x 10 <sup>10</sup> cm <sup>-3</sup> (at 300 K)                                                              |  |

| Electrical properties    | Electron mobility Hole mobility         | ≤1400 cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup><br>≤450 cm <sup>2</sup> V <sup>-1</sup> s <sup>-1</sup> |  |

|                          | Diffusion coefficient of electron       | $\leq$ 36 cm <sup>2</sup> /s                                                                                  |  |

|                          | Diffusion coefficient of hole           | $\leq$ 12 cm <sup>2</sup> /s                                                                                  |  |

| Optical properties       | Absorption Coefficient α <sub>n</sub>   | $10^{-18}.n_0.\lambda^2$ (at 300 K,                                                                           |  |

|                          |                                         | λ≥ 5μm)                                                                                                       |  |

|                          | Melting Point                           | 1412 °C                                                                                                       |  |

| Thermal properties       | Thermal Conductivity                    | 149 W.m <sup>-</sup> 1.K <sup>-1</sup>                                                                        |  |

|                          | Thermal diffusivity                     | $0.8 \text{ cm}^2/\text{s}$<br>$2.6 \times 10^{-6} \text{K}^{-1}$                                             |  |

|                          | Thermal Expansion<br>Coefficient        | $2.6 \times 10^{-6} \text{K}^{-1}$                                                                            |  |

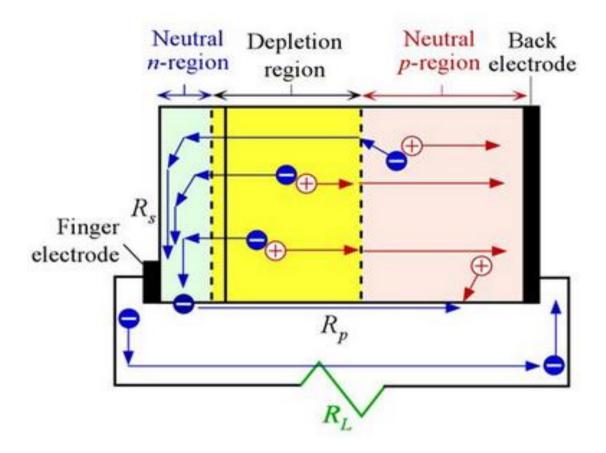

## 1.7 Principle of solar cell operation

A solar cell is a simple device: just a p-n junction with light shining on it. To maximize efficiency we need to maximize the generation of e-h pairs and minimize the recombination of e-h pairs. For the case of p-n junction diode under dark condition: anytime an electron and hole recombine anywhere within the diode, one electron flows in the external circuit. For the case of p-n junction diode under light: anytime an electron and hole pairis generated within the diode, one electron flows in the external circuit [28].

Figure 1.8 Working principle of solar cell

### 1.8 Efficiency of silicon solar cell

Solar cell efficiency refers to the portion of sunlight energy that can be converted into electricity via photovoltaic. Since January 1993, Progress in Photovoltaic has published six monthly listings of the highest confirmed efficiencies for a range of photovoltaic cell and module technologies [29, 30, 31]. Here mentioned results up to 2014, published in the solar cell efficiency table (version 44) [32] shown in table 1.2.

Table 1.2 Highest confirmed terrestrial solar cell efficiency measured under AM1.5 spectrum

| Classification of solar cell | Efficiency     | Description                   | References |

|------------------------------|----------------|-------------------------------|------------|

|                              | (%)            |                               |            |

| Silicon (Crystalline)        | 25.6±0.5       | Panasonic (HIT structure)     | [33]       |

| Silicon (Multi crystalline)  | 20.4±0.5       | FhG-ISE                       | [34]       |

| Silicon (amorphous)          | 10.1±0.3       | Oerlikon Solar Lab,           | [35]       |

| Silicon (Micro crystalline)  | 11.0±0.3       | Neuchatel                     | [36]       |

| Si (large multi crystalline) | $19.5 \pm 0.4$ | AIST                          | [37]       |

| III-V GaAs Thin film         | 28.8±0.9       | Q-Cells, laser-fired contacts | [38]       |

| CIGS thin film cell          | 20.5±0.6       | Alta device                   | [39]       |

| Dye sensitised cell          | 11.9±0.4       | Solibro, on glass             | [40]       |

| Silicon (mini module)        |                | Sharp                         | [41]       |

|                              | 10.5±0.3       | CSG solar (<2μm on glass,     |            |

|                              |                | 20 cells)                     |            |

#### 1.9 Review of Literature

The foundation for PV device operation and improvements was formulated in the period from 1905 to 1950. The key events in this period were Einstein's photon theory, Czochralski crystal growth method for single crystal silicon and germanium growth and the development of band theory for high purity single crystal semiconductors [42, 43, 44, 45].

In 1940, Russell Shoemaker Ohl, researcher at Bell Laboratory noticed that current had flown in a particular cracked silicon sample when it was exposed to light. Ohl had inadvertently made a p-n junction and the crack probably formed between the boundary of p and n region. Ohl patented (US Patent 2402662, "Light sensitive device") his solar cell in 1946, which was about one percent efficient [46].

The first practical single crystal silicon solar cell was created in 1954 at Bell Laboratories by Pearson, Chapin, and Fuller. They faced the problem of making good electrical contact and the impurity material. Later they solve those problems and made

boron-arsenic silicon sells. Those first silicon solar cells were about 6 percent efficient. Pearson, Chapin, and Fuller had patented (patent US2780765, "Solar Energy Converting Apparatus) their solar cell in 1957, which was about eight percent efficient [47, 48].

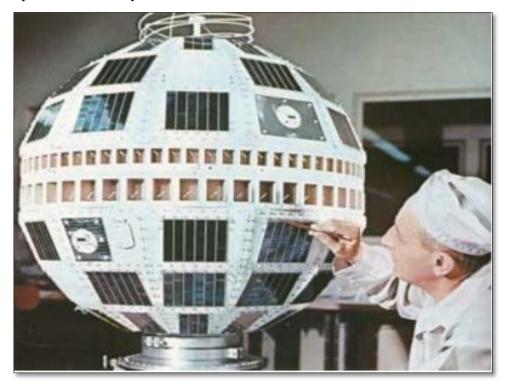

First applications of PV solar cells were on space satellites, later for initial terrestrial applications. First Telstar communication satellite launched in 1962 which was powered by silicon solar cells is shown in figure 1.9[49]. In 1970s, silicon cells were evolved for use in terrestrial installations. The foundation was then laid for the development of a variety of markets for PV solar cells.

Figure 1.9Telstar communication satellite [50]

The international participation in PV cell deployment from 2000 to present was shifted from US to Germany, China, and Japan. German Renewable Energy Sources Act creates a Solar Feed-In-Tariff (FIT) which creates a solar market in Europe [51]. Suntech Power is then formed in China in 2001 [52]. In 2011, fast-growing factories in China push manufacturing costs down to about \$1.25 per watt for silicon photovoltaic modules [53].

The standard industrial solar cell production is mainly carried out on boron doped mono-crystalline or Cz Si wafers in 1951 [54]. The thinner wafer of 150 to200 µm is introduced with active cell area of 125x125 mm² or 156x156 mm² in 2010 [55]. Industrial processing steps are- the saw damage etching, both side texturing by wet

chemical etching, phosphorous emitter diffusion by POCl<sub>3</sub>, HF cleaning, the edge isolation, the front surface iscoated with SiN<sub>x</sub>:H anti-reflection and passivation layer, contact formation by screen printing where silver (Ag) containing front contact and the rear side is typically fully covered by an aluminium (Al) based paste [56]. Note that SiN<sub>x</sub>:H film is an excellent surface passivator and a very good AR coating material. Whereas SiO<sub>2</sub> film is an excellent surface passivator and AR coating performances is slightly lower compared to SiN<sub>x</sub>:H film; the overall performance is good [57]. The wafers then go through co-firing step, where the front contact paste etches through the SiN<sub>x</sub>:H layer and establishes contact to the emitter. Simultaneously on the rear side the Aluminium BackSurface Field (Al-BSF) is formed. Additionally, the hydrogen-rich SiN<sub>x</sub> layer releases hydrogen during the firing step which can passivate defects in the Si crystal. The efficiencies obtained with this type of process in industry today are up to 19.2% for mono (Cz) Si wafers (including a selective emitter structure)[58]. In average, efficiencies above 17% for standard mc Si and above 18% for Cz Si are possible [59].

At present, in order to reduce cost, various researches are ongoing for the improvement of fabrication and characterization process for commercial solar cell production. In 2010, Vikram*et al.*at the University of Virginia,reported a simplified single step process for Cz and Fz- substrate of c-Si photovoltaic device fabrication. Single step incorporates the thin film of phosphorus doped spin on dopant (SOD) serves as dopant source, anti-reflection coating (ARC) and a surface passivation layer. They have reported the conversion efficiency of over 15% [60].

Plasma Enhanced Chemical Vapor Deposition (PECVD) equipment is widely used in SiNx:H film surface passivation and ARC coating in the industrial fabrication process. But the concept of simplified fabrication process gives the idea of SiO<sub>2</sub> film as surface passivator and ARC on mc-silicon solar cells [60]. This will helps to avoid costly equipment PECVD, avoid the using HF, and reduce the processing steps as well as process monitor steps. Less production cost can be hearten and accelerated the expansion of production into radical levels. Moreover, the toxic silane gas can be avoided which gives rise the environment friendly fabrication.

The measurements on solar cell wafers yield unreliable values for commercial aspects. Hence, in most cases, the solar cell industry uses additional "control wafers (dummy)" in each process step that are polished on one side. Another important issue is measurements are made on small areas. In solar cell monitoring, it is important that

the properties of the entire wafer be measured because of non-uniformities. Most of the cases the measurement equipments are expensive [61]. The major process steps, parameters are monitored by different techniques. The list of the major process steps, parameters that are monitored are given in the following table 1.3.

Table 1.3 Major process steps, parameters and the monitoring techniques used in solar cell fabrication [61]

| Process or monitor step     | Parameters        | Technique                 |

|-----------------------------|-------------------|---------------------------|

| Crystal growth (ingot       | τ                 | PCD                       |

| quality)                    |                   |                           |

| Wafer cleanliness           | Surface roughness | Reflecteance              |

| Texturing                   | Texture height    | SEM/ Optical              |

|                             |                   | microscopy/ Reflectance   |

| Electronic quality of wafer | $L/\tau$          | SPV/ PCD                  |

| Junction depth              | Sheet resistance  | 4 point probe/ groove     |

|                             |                   | and stain                 |

| Defect Density              | Dislocation       | Chemical Delineation /    |

|                             | Density           | TEM                       |

| Impurity Concentration      |                   | FTIR, NAA, SPV, DLTS      |

| AR-Coating                  | Thickness,        | Ellipsometer/Interference |

|                             | Refraction Index  |                           |

| Metallization               | Line Width        | Optical/SEM               |

| I-V of Cell                 | Voc, Jsc, FF      | Standard I-V              |

|                             |                   | measurement               |

### 1.10 Organization of thesis

This thesis is organized first with a brief introduction into the photovoltaics history, its market potential and the current status of commercialmono-crystalline silicon solar cell in photovoltaic industry. Chapter 2 is a summary of theory and instrumentation techniques of characterization tool. Chapter 3 follows the characterization of the silicon wafers such as type measurement, thickness measurement, physical and sheet resistance measurement etc. This chapter also discussed about the low cost in-house made hot probe technique and took some characteristic curves from this tool. It also covers the carrier concentration changes inside the wafers due to thermal effect. Chapter 4 follows the properties of isotropic and anisotropic etched samples. It follows the p-type etched silicon samples thickness measurement, 2D optical microscopy, SEM imaging, stylus surface profiling for structural characterization, optical characterization through spectroscopic reflectometer and SRM. Chapter 5 is a summary of atmospheric pressure chemical vapour deposition (APCVD) diffusion process with single step for doping and surface passivation and ARC. Spin on doping is also discussed here. It follows the properties of phosphorus doped emitter layer on the boron doped silicon wafer. It covers the polarity measurement, doping uniformity measurement, SEM imaging, compositional analysis by EDS, optical reflectance measurement, sheet resistance measurement and ARC film thickness measurement. Chapter 6 discusses the surface photovoltage measurement. It covers the measurements of minority carrier diffusion length, minority carrier lifetime, carrier generation and recombination inside the three regions of solar cell. It also discusses the conversion efficiency measurement technique. It covers the measurements of open circuit voltage, short circuit current, fill factor, efficiency, maximum voltage, maximum current and maximum power.

#### 1.11 References

- [1] https://en.wikipedia.org/wiki/World\_energy\_resources

- [2] https://en.wikipedia.org/wiki/World\_energy\_consumption

- [3]https://www.google.com.bd/search?q=images+for+world+energy+consumption&b iw=1242&bih=602&noj=1&site=webhp&tbm=isch&imgil=1QY0WK1wTlgDd M%253A%253B4muqU-

- ZjyFxnBM%253Bhttps%25253A%25252F%25252Fen.wikipedia.org%25252Fw iki%25252FRenewable\_energy&source=iu&pf=m&fir=1QY0WK1wTlgDdM%253A%252C4muqU-ZjyFxnBM%252C\_&usg=\_\_-luEjtS6e1Dtxa0\_\_sB0SJ-ymUY%3D&ved=0ahUKEwinxaOPq9XPAhUFrI8KHZjeCUwQyjcINQ&ei=5TX-V-e-LYXYvgSYvafgBA#imgrc=1QY0WK1wTlgDdM%3A

- [4]http://data.worldbank.org/indicator/EG.USE.COMM.FO.ZS?end=2013&start=201 3&view=map&year=1971

- [5]http://data.worldbank.org/indicator/EG.USE.COMM.FO.ZS?end=2013&start=201 3&view=map&year=2013

- [6] Pollution From Chinese Coal Casts a Global Shadow, June 11, 2006, The Newyork Times

- [7]http://data.worldbank.org/indicator/EG.USE.COMM.CL.ZS?end=2013&start=201 3&view=map&year=2013

- [8]https://www.google.com.bd/search?q=potential+of+renewable+energy+images&es pv=2&biw=1093&bih=530&tbm=isch&imgil=VI36Fha7Ran8iM%253A%253 BATB4FnhW4MzgvM%253Bhttp%25253A%25252F%25252Fenergypost.eu %25252Freality-check-renewable-energy-potential%25252F&source=iu&pf=m&fir=VI36Fha7Ran8iM%253A%252CA TB4FnhW4MzgvM%252C\_&usg=\_\_il3ooeYbVR3codbO0lcArR2o0-w%3D&ved=0ahUKEwjOq9OxkefQAhWGf7wKHbuZC-YQyjcISA&ei=tKZKWM6BE4b\_8QW7s66wDg#imgrc=zApCrBHvy\_pVsM %3A

- [9] Tester, Jefferson W.; et al. (2005). Sustainable Energy: Choosing Among Options. The MIT Press.

- [10] E. Becquerel. Comptes Rendues, 9:561, 1839.

- [11]https://en.wikipedia.org/wiki/Solar\_cell

- [12] D. M. Chapin, C. S. Fuller, and G. L. Pearson. J. Appl. Phys., 25:676, 1954

- [13] G. Raisbeck. Scientific American, 193:102, 1955.

- [14] John Perlin. From Space to Earth: The Story of Solar Electricity. Harvard University Press, 1999.

- [15] www. solarbuzz.com /facts-and-figures/ retail-price-environment/module-prices

- [16]https://www.google.com/search?q=images+of+Price+history+of+silicon+PV+cells +in+\$+per+watt&tbm=isch&imgil=OgV830F9pj-gmM%253A %253BQEwqQrwLnZJKlM%253Bhttp%25253A%25252F%25252Fwww.tomsw anton.com%25252Ftag%25252Fsolar-energy%25252F&source =iu&pf=m&fir=OgV830F9pjgmM%253A%252CQEwqQrwLnZJKlM%252C\_&usg=\_\_YDzy06wz67hLFzkzdNteOWCE0o%3D&biw=911&bih=441&dpr=1.5&ved=0ahUKEwivlPez6KjRAhVIso8KHZlOALgQyjcILg&ei=GRZtWO-jO8jkvgSZnYHACw#imgrc=OgV830F9pj-gmM%3A

- [17] www.sunpower.com

- [18] M.P Thekaekara, 'Data on oncident solar energy', Suppl. Proc. 20<sup>th</sup>Annu. Meet. Inst. Environ. Sci., 1974, P-21.

- [19] C.H. Henry, 'Limiting efficiency of ideal signal and multiple energy gap terrestrial solar cell', J. Appl. Phys. 51, 4494, 1980.

- [20] Principle conclusions of the American physical society study group on solar photovoltaic energy conversion, American physical society, New York, 1979.

- [21]https://www.google.com.bd/search?q=tables+or+images+of+classification+of+so lar+cells+with+materials+of+choices&espv=2&biw=1242&bih=602&tbm=isch &tbo=u&source=univ&sa=X&sqi=2&ved=0ahUKEwilucHH4ebQAhVFuY8K HeIjABwQsAQIFw#imgdii=GrKS1ar9UDFzqM%3A%3BGrKS1ar9UDFzqM%3A%3B01JB-4g4UUBK0M%3A&imgrc=GrKS1ar9UDFzqM%3A

- [22] D. L. Staebler and C. R. Wronski. Appl. Phys. Lett., 31:292, 1977.

- [23] Mary D. Archer and Robert Hill, editors. Clean Electricity from Photovoltaics. World Scientific, 2001.

- [24] Panasonic Press Release, 10 April 2014. Panasonic HIT® solar cell achieves world's highest energy conversion efficiency of 25.6% at research level (http://panasonic.co.jp/corp/news/official.data/data.dir/2014/04/en140410-4/en140410-4.html; accessed 24 April 2014).

- [25]M. Al-Amin and A. Assi, Efficiency improvement of crystalline silicon solar cells, Materials and Processes for Energy: Communicating Current Research and Technological Developments (2013), 22-31. Energy materials. Web. 17 Nov. 2014.

- [26] https://en.wikipedia.org/wiki/Silicon

- [27] http://www.ioffe.ru/SVA/NSM/Semicond/Si/

- [28] https://nanohub.org/resources/11942/download/2011.07.21-NCN-SC02Lundstrom.pdf

- [29] Green MA, Emery K, Hishikawa Y, Warta W, Dunlop ED. Solar cell efficiency tables (version 39). Progress in Photovoltaics: Research and Applications 2012; 20:12–20.

- [30] Green MA, Emery K, Hishikawa Y, Warta W. Solar cell efficiency tables (version 33), Progress in Photovoltaics: Research and Applications 2009; 17:85–94.

- [31] Green MA, Emery K, Hishikawa Y, Warta W, Dunlop ED. Solar cell efficiency tables (version 43). Progress in Photovoltaics: Research and Applications 2014; 22:1–9.

- [32] Green MA, Emery K, Hishikawa Y, Warta W, Dunlop ED. Solar cell efficiency tables (version 44). Progress in Photovoltaics: Research and Applications 2014

- [33] Panasonic Press Release, 10 April 2014. Panasonic HIT® solar cell achieves world's highest energy conversion efficiency of 25.6% at research level (http://panasonic.co.jp/corp/news/official.data/data.dir/2014/04/en140410-4/en140410-4.html; accessed 24 April 2014).

- [34] Schultz O, Glunz SW, Willeke GP. Multicrystalline silicon solar cells exceeding 20% efficiency. Progress in Photovoltaics: Research and Applications 2004;12: 553–558

- [35] S Benagli, D Borrello, E Vallat-Sauvain, J Meier, U Kroll, J Hötzel, Spitznagel J, Steinhauser J, Castens L, Djeridane Y. High-efficiency amorphous silicon devices on LPCVD-ZNO TCO prepared in industrial KAI-M R&D reactor.24th European Photovoltaic Solar Energy Conference, Hamburg, September 2009.

- [36] Sai H, Koida T, Matsui T, Yoshida I, Saito K,Kondo M. Microcrystalline silicon solar cells with 10.5% efficiency realized by improved photon

- absorption via periodic textures and highly transparent conductive oxide. Applied Physics Express 2013;6: 104101-1–104101-6.

- [37] Engelhart P, Wendt J, Schulze A, Klenke C, Mohr A,Petter K, Stenzel F, Hörnlein S, Kauert M, Junghänel M, Barkenfelt B, Schmidt S, Rychtarik D, Fischer M,Müller JW, Wawer P. R&D pilot line production of multi-crystalline Si solar cells exceeding cell efficiencies of 18%. Energy Procedia, 1st International Conference on Silicon Photovoltaics, Freiburg, 17–20 April, 2010 (www.Elsevier.com/locate/procedia).

- [38] Kayes BM, Nie H, Twist R, Spruytte SG, Reinhardt F, Kizilyalli IC, Higashi GS. 27.6% conversion efficiency, a new record for single-junction solar cells under 1 sun illumination. Proceedings of the 37<sup>th</sup> IEEE Photovoltaic Specialists Conference, 2011.

- [39] Osborne, M. Hanergy'ssolibro has 20.5% CIGS solar cell verified by NREL, 8 April 2014 (http://www.pv-tech.org/ news/ hanergyssolibro has 20.5 cigs solar cell verified by nrel; accessed 24 April 2014).

- [40] Komiya R, Fukui A, Murofushi N, Koide N, Yamanaka R, Katayama H. Improvement of the conversion efficiency of a monolithic type dye-sensitized solar cell module. Technical Digest, 21st International Photovoltaic Science and Engineering Conference, Fukuoka, November 2011: 2C-5O-08

- [41] Keevers MJ, Young TL, Schubert U, Green MA. 10% Efficient CSG minimodules. 22nd European Photovoltaic Solar Energy Conference, Milan, September 2007.

- [42] Einstein, A, "On the Quantum Theory of Radiation" PhyikalischeZeitschrift 18 (1917).

- [43] David C. Brock (Spring 2006). "Useless No More: Gordon K. Teal, Germanium, and Single-Crystal Transistors". Chemical Heritage Newsmagazine (Chemical Heritage Foundation) 24 (1).Retrieved 2008-01-21.

- [44] Bloch, F, Z. Phys. (1928), 52, 555.

- [45] Wilson, A. H., Proc. Roy. Soc.A (1931), 133, 458; 134, 277.

- [46] https://en.wikipedia.org/wiki/Solar\_cell

- [47] D. M. Chapin, C. S. Fuller, and G. L. Pearson (May 1954). "A New Silicon p-n Junction Photocell for Converting Solar Radiation into Electrical Power". Journal of Applied Physics 25 (5): 676–677. doi:10.1063/1.1721711

- [48] Gerald L. Pearson, Daryl M. Chapin, and Calvin S. Fuller(AT&T) receive patent US2780765, "Solar Energy Converting Apparatus."(1957)

- [49] https://en.wikipedia.org/wiki/Telstar

- [50]https://www.researchgate.net/profile/Lewis\_Fraas/publication/274961489\_Chapte r\_1\_History\_of\_Solar\_Cell\_Development/links/552da7be0cf29b22c9c4f8b5.pdf

- [51] http://en.wikipedia.org/wiki/German\_Renewable\_Energy\_Act

- [52] http://en.wikipedia.org/wiki/Suntech\_Power

- [53]PVPS\_report\_-\_A\_Snapshot\_of\_Global\_PV\_-\_1992-2013\_-\_final\_3.pdf; http://en.wikipedia.org/wiki/Agua\_Caliente\_Solar\_Project

- [54] www.waferworld.com/czochralski-process-and-silicon-wafers

- [55]N Cheung, "Solar Cells Fabrication Technologies" Lec-26, University of California, Berkeley, EE143 F2010

- [56] vorgelegt von , Johannes Junge, "High efficiency process development for defect-rich silicon wafer materials" . Mathematisch-Naturwissenschaftliche Sektion Fachbereich Physik , University of Konstanz, Konstanzer Online- Publikations-System(Kops), Available : kops.uni konstanz.de/handle/123456789/18982

- [57] www-inst.eecs.berkeley.edu/~ee143/fa10/lectures/Lec\_26

- [58] B.S. Tjahjono et al., "Optimizing selective emitter technology in one year of full scale production", *Proc. of the 26th EU PVSEC*, 2011, pp. 901-906.

- [59] P. Wawer, J. Mueller, M. Fischer, P. Engelhart, A. Mohr, and K. Petter, "Latest trends in development and manufacturing of industrial, crystalline silicon solarcells", *Energy Procedia*, **8**, pp. 2-8, 2011.

- [60] V. V. Iyengar, B. K. Nayakk and M.C. Gupta, Silicon PV devices based on a single step for doping, anti-reflection and surface passivation, Solar Energy Materials & Solar Cells 94 (2010), 2205-2211, journal homepage: www.elsevier.com/locate/solmat

- [61] B. Sopori, Y. Zhang, and W. Chen, "Process Monitoring in Solar Cell Manufacturing", National Renewable Energy Laboratory, NREL/CP-520-26887, October 1999

## **Chapter II**

# **Characterization Techniques**

#### 2.1 Introduction

This chapter briefly describes the characterization techniques used to study the properties of p-type and n-type silicon for photovoltaic application. Methodology and theoretical aspects related to morphological, structural, optical, and electrical characterization techniques are discussed. Brief discussion on energy dispersive x-ray spectrography for compositional analysis, surface photo voltage near infrared spectroscopy is also presented. Brief descriptions of instrumentation setup are also explained in this chapter.

#### 2.2 Measurement of thickness