Thesis for the Degree of Doctor of Philosophy

# Design and Implementation of Reversible Programmable Devices

Registration No: 174/2015 - 2016

Department of Computer Science and Engineering

University of Dhaka

Dhaka, Bangladesh

December 2019

### Thesis for the Degree of Doctor of Philosophy

# Design and Implementation of Reversible Programmable Devices

Nazma Tara

Department of Computer Science and Engineering

University of Dhaka

Dhaka, Bangladesh

December 2019

# Design and Implementation of Reversible Programmable Devices

By

Nazma Tara

Registration No: 174/2015 - 2016

Supervised by

Moinul Islam Zaber, Ph.D.

Prof. Hafiz Md. Hasan Babu, Ph.D.

Submitted to the Department of Computer Science and Engineering of the Faculty of the Engineering and Technology in University of Dhaka for partial fulfillment of the requirements of the degree of Doctor of Philosophy

**Dissertation Committee:**

Prof. Md. Abdul Mottalib, Ph.D. (Convener)

Prof. Nazrul Islam Mondal, Ph.D. (External Member)

Moinul Islam Zaber, Ph.D. (Supervisor)

# Design and Implementation of Reversible Programmable Devices

By

Nazma Tara

Registration No: 174/2015 - 2016

Supervised by

Moinul Islam Zaber, Ph.D.

Prof. Hafiz Md. Hasan Babu, Ph.D.

Submitted to the Department of Computer Science and Engineering of the Faculty of the Engineering and Technology in University of Dhaka for partial fulfillment of the requirements of the degree of Doctor of Philosophy

**Declaration**

We declare that this thesis titled "Design and Implementation of Reversible Pro-

grammable Logic Devices" and the works presented in it are our. We confirm

that:

■ The full part of the work is done during Ph.D. research study in University

of Dhaka, Bangladesh.

■ Any part of this thesis has not previously been submitted for a degree or

any other qualification in this University or any other institution.

■ We have consulted the published works of others with appropriate references.

■ This thesis work is done entirely by us and our contributions and enhance-

ments from other works are stated.

| Signed:                            |

|------------------------------------|

|                                    |

| Candidate                          |

| Countersigned:                     |

| Supervisor: Dr. Moinul Islam Zaber |

Co-supervisor: Dr. Hafiz Md. Hasan Babu

i

## Abstract

Reversible logic is a computing design, where the ideal implementation would produce zero entropy gain. This unique feature causes the prominent use of reversible computing. More integration capability and regular structure for synthesizing a large number of logic functions made programmable devices enthusiastic to use.

In this thesis, we describe efficient design procedures of two programmable devices namely Programmable Logic Array (PLA) and Field Programmable Gate Array (FPGA) with reversible logic gate.

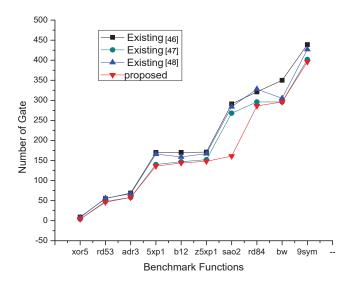

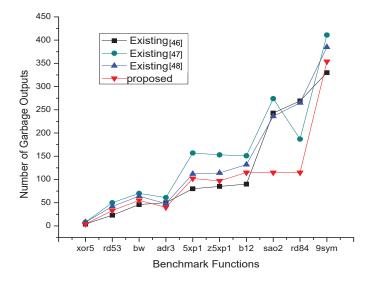

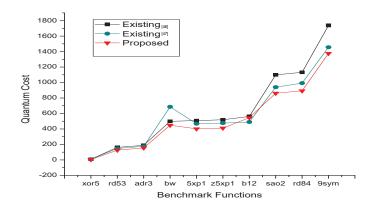

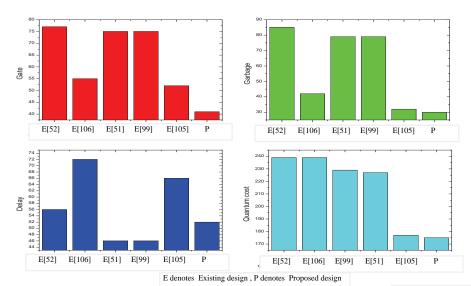

In the first part of this thesis, we design the reversible Programmable Logic Array (RPLA). Here, we propose an efficient algorithm to design the RPLA with a newly proposed 3 × 3 reversible TB (Tara-Babu) gate, which can realize multi-output ESOP (Exclusive-OR Sum of Product) functions. We present a heuristic algorithm to sort and realize the product terms of ESOP functions to share the internal sub-products to reduce the number of gates in the proposed RPLA. Proposed algorithms make the RPLA more efficient with improvement of 9.83% in terms of the number of gates, 21.3% in terms of the number of garbage outputs and 14.75% in terms of quantum cost than the counter metrics of the existing RPLA averagely. Moreover, we compute the area requirement and the power consumption of the proposed RPLA. We also analyze the performances by using MCNC benchmark functions.

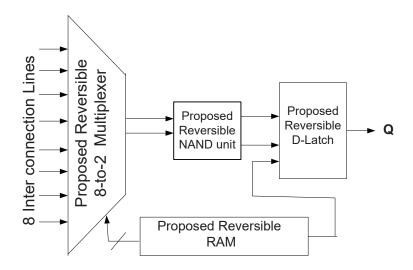

In the last part of this thesis, we design the most significant part of a Field Programmable Gate Array, the Plessey Logic Block with reversible gate. On the way to design the proposed reversible Plessey Logic Block, we design each component such as reversible D-Latch, reversible Decoder, reversible Multiplexer, reversible Master-Slave Flip-Flop, and reversible RAM separately. The proposed design of the individual component is primarily made efficient in terms of the number of

gates, garbage outputs, quantum cost, and delay. In addition, area and power are reduced to ensure the power efficiency of the circuits. Two  $4 \times 4$  reversible gates, namely HNF (Hafiz-Naz-Flip-Flop) gate and HND (Hafiz-Naz-Decoder) gate are proposed to achieve the optimization goal. Moreover, proposed algorithms, lemmas and theorems certify the novelty of the proposed design. Compared to previous works, the proposed counter-parts of Reversible Plessey Logic Block require less number of gates, garbage outputs, quantum cost, and delay. Finally, the proposed Reversible Plessey (4  $\times$  2) Logic Block is compared with existing designs. The Comparative results prove the efficacy and novelty of the proposed design showing improvement of 51.62% in terms of number of Transistor, 73.57% in terms of area requirement and 34.12% in terms of power consumption with respect to the corresponding metrics of the best existing design in the literature.

Dedicated to Those People

Who are Honest, Spiritual and Patriot

Who Work for the Welfare of Human Being

## Acknowledgements

Praise be to Allah, Lord of the universe, most gracious, most merciful. No one can anything without his blessings.

My deepest thanks and gratitude to Dr. Moinul Islam Zaber and Prof. Dr. Hafiz Md. Hasan Babu, for suggesting the topic of this thesis, and their kind supervision. It is a great honor to work under their supervision. Their guidance, encouragement and confidence in me has transformed me into a better researcher. I am conveying my gratefulness to them for facilitating the work environment also.

I am indebted to the CSE department faculties, especially Prof. Dr. Sabbir Ahmed, Prof. Dr. Md. Abdur Razzaque, Dr. Asif Hossain Khan, Dr. Mamunur Rashid, Abu Ahmed Ferdous and CSE department staffs for helping me to finish the long journey successful. A special thanks to Dr. Ahsan Raja Chowdhury, former faculty of CSE department, who is my mentor in this research area.

It is a great opportunity for me to be a member of the VLSI Research Group, Department of Computer Science and Engineering, University of Dhaka. Along the way, a great support comes directly or indirectly from every single group member. I also thank the members of other groups for their cordial help, support, suggestions during the whole period of research. Thanks go to my fellow researchers Dr. Lafifa Jamal, Dr. Selina Sharmin and other researchers Md. Samsujjoha, Md. Mubin Ul Haque and Zarrin Tasnim Sworna. Their direct support, inspiring words and comments was appreciative.

I must thank the ministry of ICT of Government of the People's Republic of Bangladesh for the innovation fund of research.

Hartiest thanks to my husband S.M. Bashir Ahmed, sons S.M.F. Imbesat Ahmed and S.M.N. Intesar Ahmed who continue assist me till the end of the journey. Their support, understanding, encouragement and sacrifice make this thesis possible. I am also deeply indebted to my mother Rokeya Begum, father Shah Md. Monsur Ali, mother-in-law Rehana Begum and father-in-law S. M. Mansur Ahmed, whose

affection, love, encouragement and prayers of day and night make me able to finish the research. My other family members also show their continuous support during this hard time.

> Nazma Tara December 2019

## Contents

| D        | eclar  | ation o | of Author    | rship                                                             | i   |

|----------|--------|---------|--------------|-------------------------------------------------------------------|-----|

| A        | bstra  | ıct     |              |                                                                   | ii  |

| A        | ckno   | wledge  | ements       |                                                                   | v   |

| Li       | ist of | Figur   | es           |                                                                   | X   |

| Li       | ist of | Table   | 5            |                                                                   | xii |

| 1        | Intr   | oducti  | ion          |                                                                   | 1   |

|          | 1.1    | Metho   | dologies of  | f this Research                                                   | 4   |

|          | 1.2    | Challe  | enges of thi | is Research                                                       | 5   |

|          | 1.3    | Contr   | ibutions of  | this Research                                                     | 5   |

|          | 1.4    | Organ   | ization of   | the Dissertation                                                  | 7   |

| <b>2</b> | Bac    | kgrou   | nd Studie    | es                                                                | 9   |

|          | 2.1    | Introd  | uction       |                                                                   | 9   |

|          | 2.2    | Basic   | Definitions  | s in Reversible Logic                                             | 12  |

|          |        | 2.2.1   | Reversibl    | e Gate                                                            | 12  |

|          |        | 2.2.2   | Garbage      | Output                                                            | 15  |

|          |        | 2.2.3   | Quantum      | a Cost                                                            | 15  |

|          |        | 2.2.4   | Delay .      |                                                                   | 18  |

|          |        | 2.2.5   | More abo     | out Reversible Gates                                              | 19  |

|          |        |         | 2.2.5.1      | Feynman Gate (CNOT Gate or Ex-OR Gate) $\ . \ . \ .$              | 20  |

|          |        |         |              | Feynman Double Gate (F2G) $\dots \dots \dots$                     | 20  |

|          |        |         |              | Toffoli Gate (TG)                                                 | 21  |

|          |        |         | 2.2.5.4      | Peres Gate (PG) $\dots$                                           | 22  |

|          |        |         |              | Fredkin Gate (FRG) $\ \ldots \ \ldots \ \ldots \ \ldots \ \ldots$ |     |

|          |        |         |              | Modified Fredkin Gate (MFRG)                                      | 24  |

|          | 2.3    | Physic  | cal Implem   | entation Methodologies of Reversible Logic Circuits               | 24  |

*Contents* viii

|   | 2.4 | Overview of Programmable Logic Devices                           | 25        |

|---|-----|------------------------------------------------------------------|-----------|

|   |     | 2.4.1 Classification of PLDs                                     | 27        |

|   |     | 2.4.2 The General Architecture of Programmable Logic Array (PLA) | 27        |

|   |     | 2.4.3 The General Architecture of FPGA                           | 29        |

|   | 2.5 | Summary                                                          | 31        |

| 3 | Rev | ersible Programmable Logic Array                                 | 32        |

|   | 3.1 | Introduction                                                     | 32        |

|   | 3.2 | Contribution                                                     | 33        |

|   | 3.3 | Organization of the Chapter                                      | 33        |

|   | 3.4 | Related Works on RPLA                                            | 34        |

|   | 3.5 | Proposed RPLA                                                    | 36        |

|   |     | 3.5.1 Proposed Reversible Tara-Babu (TB) Gate                    | 36        |

|   |     |                                                                  | 38        |

|   |     | 3.5.3 Proposed Ex-OR-plane of RPLA                               | 40        |

|   | 3.6 |                                                                  | 41        |

|   | 3.7 |                                                                  | 47        |

|   |     |                                                                  | 47        |

|   |     |                                                                  | 48        |

|   |     |                                                                  | 48        |

|   |     |                                                                  | 51        |

|   | 3.8 | ·                                                                | 56        |

| 4 | Rev | ersible Field Programmable Gate Array                            | <b>58</b> |

|   | 4.1 | · ·                                                              | 58        |

|   | 4.2 |                                                                  | 59        |

|   | 4.3 |                                                                  | 60        |

|   | 4.4 |                                                                  | 60        |

|   | 4.5 | Design Methodology                                               | 61        |

|   | 4.6 |                                                                  | 61        |

|   |     |                                                                  | 62        |

|   |     | •                                                                | 65        |

|   |     |                                                                  | 66        |

|   |     | •                                                                | 73        |

|   |     | ·                                                                | 78        |

|   |     |                                                                  | 80        |

|   | 4.7 | •                                                                | 80        |

|   | 4.8 | · ·                                                              | 83        |

|   |     |                                                                  | 84        |

|   |     |                                                                  | 84        |

|   |     |                                                                  | 87        |

|   |     |                                                                  | o.<br>88  |

Contents

|              |                            | 4.8.4.1        | Performance of Proposed Reversible D-Latch        | . 88  |  |

|--------------|----------------------------|----------------|---------------------------------------------------|-------|--|

|              |                            | 4.8.4.2        | Performance of Proposed Reversible Master-Slave   |       |  |

|              |                            |                | Flip-Flop                                         | . 89  |  |

|              |                            | 4.8.4.3        | Performance of Proposed Reversible Decoder        | . 90  |  |

|              |                            | 4.8.4.4        | Performance of Proposed Reversible Multiplexer .  | . 91  |  |

|              |                            | 4.8.4.5        | Performance of Proposed Reversible RAM            | . 92  |  |

|              |                            | 4.8.4.6        | Other Performance analysis of Plessey Logic Block | 92    |  |

|              | 4.9                        | Summary        |                                                   | . 98  |  |

|              |                            |                |                                                   |       |  |

| 5            | Con                        | clusions       |                                                   | 99    |  |

|              | 5.1                        | Summary of F   | Research                                          | . 99  |  |

|              | 5.2                        | Future Work .  |                                                   | . 101 |  |

|              |                            |                |                                                   |       |  |

| A            | Var                        | ious Existing  | Reversible gates                                  | 116   |  |

| В            | Tra                        | nsistor Realiz | ation of Proposed Reversible gates                | 118   |  |

|              |                            |                |                                                   |       |  |

| $\mathbf{C}$ | List                       | of Acronyms    | 3                                                 | 120   |  |

| П            | T ist                      | of Dublication | nng                                               | 122   |  |

| ע            | D List of Publications 122 |                |                                                   |       |  |

# List of Figures

| 2.1  | Ex-OR function representations by block diagram and logical symbol. | 12 |

|------|---------------------------------------------------------------------|----|

| 2.2  | $n\times n$ reversible gate                                         | 12 |

| 2.3  | Block diagram Toffoli gate                                          | 13 |

| 2.4  | Bijection properties of Toffoli gate                                | 14 |

| 2.5  | Universal properties of Toffoli gate                                | 14 |

| 2.6  | Basic quantum gates and their symmetric patterns                    | 15 |

| 2.7  | Quantum circuit of Toffoli gate                                     | 16 |

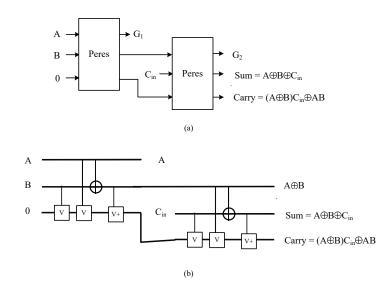

| 2.8  | Reversible full-adder1 (a) Block diagram (b) Quantum circuit        | 16 |

| 2.9  | Reversible full-adder2 (a) Block diagram (b) Quantum circuit        | 17 |

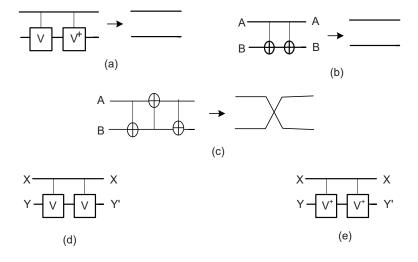

| 2.10 | Rules in minimization of quantum circuit                            | 17 |

| 2.11 | Delay assessment of reversible gates                                | 19 |

|      | Feynman gate                                                        | 20 |

| 2.13 | Feynman Double gate                                                 | 21 |

| 2.14 | Popular reversible gates                                            | 22 |

| 2.15 | Transistor level realization of AND and OR gate                     | 25 |

|      | Transistor level realization of reversible gate [74]                | 26 |

| 2.17 | Classification of the Programmable Logic Devices                    | 27 |

| 2.18 | The architecture of irreversible Programmable Logic Array           | 28 |

| 2.19 | Different parts of an FPGA                                          | 30 |

| 3.1  | Proposed reversible TB gate : (a)block diagram (b) quantum circuit. | 36 |

| 3.2  | Implementation of all boolean functions using the proposed re-      |    |

|      | versible TB gate                                                    | 37 |

| 3.3  | Different AND terms produced simultaneously by the proposed TB      |    |

|      | gate                                                                | 38 |

| 3.4  | Different combinations of the F2G and TB gates                      | 38 |

| 3.5  | The proposed AND-plane of RPLA for multi-output ESOP func-          |    |

|      | tions given in Equ. 3.7                                             | 42 |

| 3.6  | The Proposed Ex-OR plane of RPLA for multi-output ESOP func-        |    |

|      | tions given in Equ. 3.7                                             | 44 |

| 3.7  | The proposed reversible Programmble Logic Array for Equ. 3.7        | 45 |

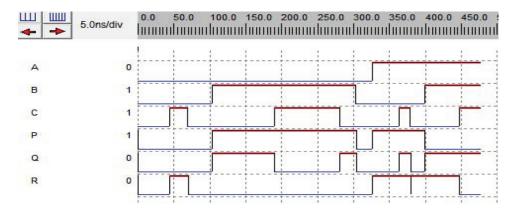

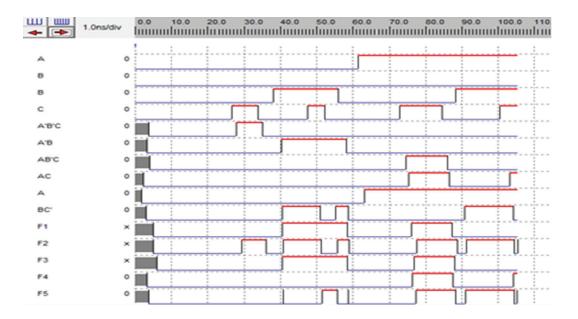

| 3.8  | Simulation of the proposed TB gate                                  | 48 |

List of Figures xi

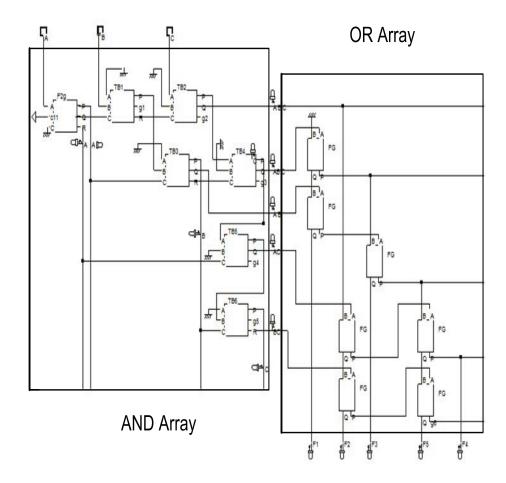

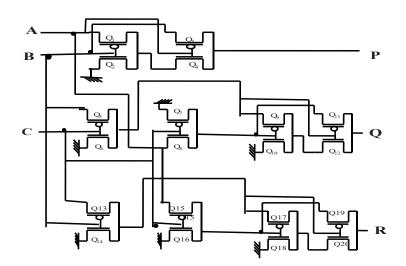

| 3.9  | Architecture of the proposed RPLA for ESOP functions given in Equ. 3.7 at physical-lavel in DSCH 3.5 [93] | 49  |

|------|-----------------------------------------------------------------------------------------------------------|-----|

| 3.10 | Simulation of the proposed RPLA for ESOP functions (Equ. 3.7).                                            | 50  |

| 3.11 | Graphical representations of Benchmark functions vs Number of                                             |     |

|      | gates                                                                                                     | 55  |

| 3.12 | Graphical representations of Benchmark functions vs Number of                                             |     |

|      | Garbage outputs                                                                                           | 55  |

| 3.13 | Graphical representations of Benchmark functions vs Quantum cost.                                         | 56  |

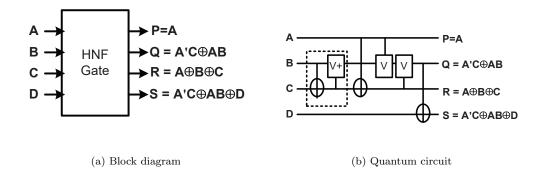

| 4.1  | The proposed reversible HNF gate                                                                          | 63  |

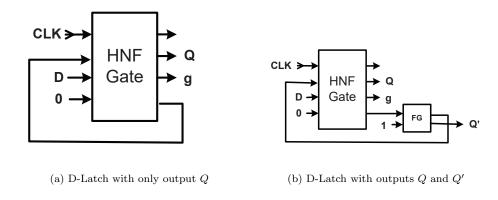

| 4.2  | The proposed design of D-Latch                                                                            | 63  |

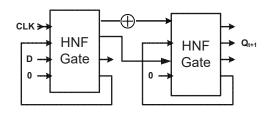

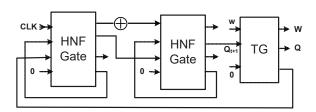

| 4.3  | The proposed design of reversible Master-Slave D-Flip-Flops                                               | 65  |

| 4.4  | The proposed reversible HND gate and its application                                                      | 67  |

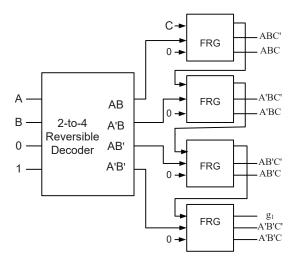

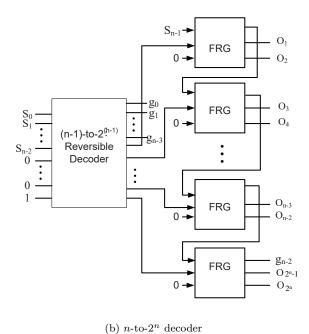

| 4.5  | The designs of the proposed reversible decoders                                                           | 70  |

| 4.6  | The Proposed architecture of reversible RAM for Plessey FPGA                                              | 74  |

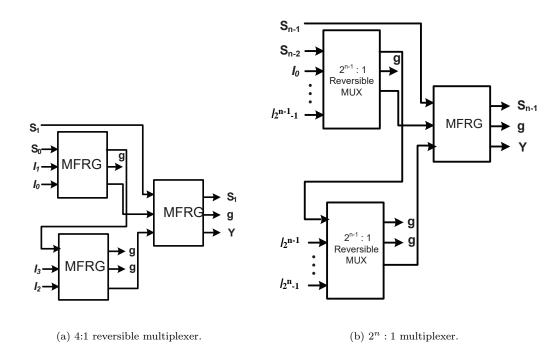

| 4.7  | Modified Fredkin gate as reversible 2:1 multiplexer                                                       | 78  |

| 4.8  | the proposed designs of reversible multiplexers                                                           | 79  |

| 4.9  | The proposed reversible NAND unit of Plessey Logic Block                                                  | 80  |

| 4.10 | Proposed Reversible Plessey Logic Block of FPGA                                                           | 82  |

| 4.11 | , , ,                                                                                                     |     |

|      | proposed reversible components                                                                            | 84  |

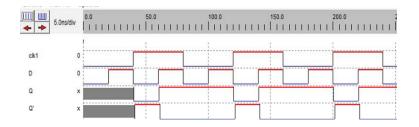

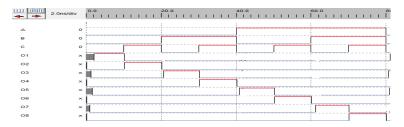

|      | Simulation of the proposed reversible D-Latch                                                             | 85  |

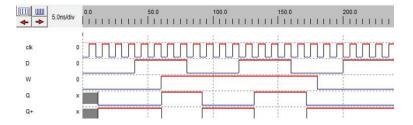

| 4.13 | Simulation of the proposed reversible write enable Master-Slave                                           |     |

|      | Flip-Flop.                                                                                                | 85  |

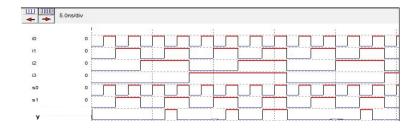

|      | Simulation of the proposed reversible 4:1 Multiplexer                                                     | 86  |

|      | Simulation of the proposed reversible 2-to-4 Decoder                                                      | 86  |

|      | Simulation of the proposed reversible 3-to-8 Decoder                                                      | 86  |

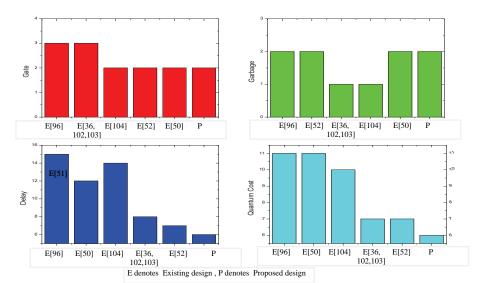

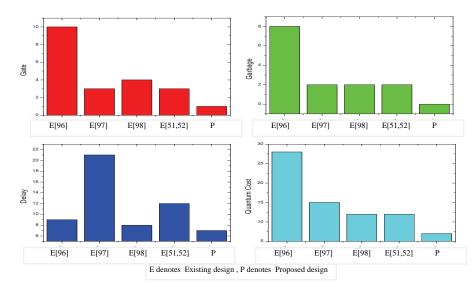

| 4.17 | Performance analysis of different reversible Flip-Flops with simul-                                       | ~ ~ |

|      | taneous Q and Q' output                                                                                   | 95  |

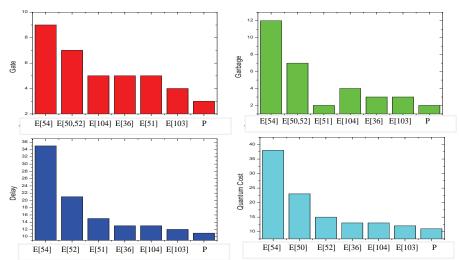

|      | Performance analysis of different reversible Master-Slave Flip-Flops                                      | 95  |

|      | Performance analysis of different reversible 2-to-4 decoders                                              | 96  |

|      | Performance analysis of different reversible 4:1 multiplexers                                             | 96  |

| 4.21 | Performance analysis of different reversible $4 \times 2$ RAMs in terms of                                | 07  |

|      | gate and garbage                                                                                          | 97  |

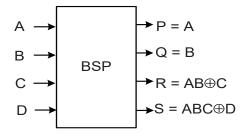

| A.1  | Block diagram of BSP gate                                                                                 | 116 |

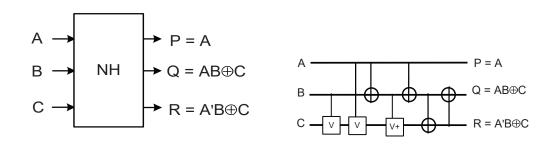

| A.2  | NH gate                                                                                                   | 116 |

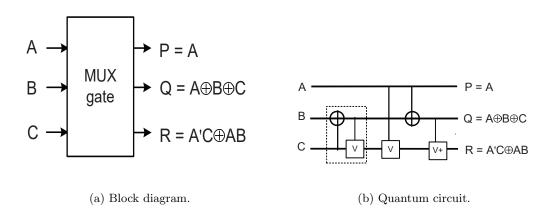

| A.3  | MUX gate                                                                                                  |     |

| B.1  | Transistor realization of the proposed TB gate                                                            | 118 |

| B.2  | Transistor realization of the proposed HND gate                                                           | 119 |

| B.3  | Transistor realization of the proposed HNF gate                                                           |     |

## List of Tables

| 2.1        | Truth table method                                                                                                       | 9   |

|------------|--------------------------------------------------------------------------------------------------------------------------|-----|

| 2.2        | Truth table for a 3-input 3-output function                                                                              | 10  |

| 2.3        | Reversible function computing the logical Ex-OR                                                                          | 11  |

| 2.4        | Reversible function computing the logical AND                                                                            | 11  |

| 2.5        | Truth table of NOT gate                                                                                                  | 13  |

| 2.6        | Truth table of reversible Toffoli gate                                                                                   | 13  |

| 3.1        | Truth table of the proposed reversible TB gate                                                                           | 37  |

| 3.2        | Frequency table for the ESOP functions in Equ. 3.7                                                                       | 41  |

| 3.3        | Comparison of the proposed and the existing RPLA for the ESOP                                                            |     |

|            | functions in Equ. 3.7                                                                                                    | 51  |

| 3.4        | Comparison of the proposed and the existing RPLAs by using MCNC Benchmark functions in terms of the total number of gate | 52  |

| 3.5        | Comparison of the proposed and the existing RPLAs by using MCNC                                                          |     |

|            | Benchmark functions in terms of the total number of garbage outputs)                                                     | 53  |

| 3.6        | Comparison of the proposed and the existing RPLAs by using MCNC                                                          |     |

| a <b>-</b> | Benchmark functions in terms of quantum cost)                                                                            | 54  |

| 3.7        | Area requirement and power consumption of the different MCNC                                                             | F 1 |

|            | benchmark circuits by using the proposed method                                                                          | 54  |

| 4.1        | The characteristic table of the D-Latch                                                                                  | 62  |

| 4.2        | Truth table of the proposed reversible HNF (Hasan-Naz-Flip-Flop)                                                         |     |

|            | gate                                                                                                                     | 64  |

| 4.3        | Truth table of the proposed reversible HND (Hasan-Naz-Decoder) gate                                                      | 68  |

| 4.4        | Function of $S_0$ and $S_1$ select lines                                                                                 | 79  |

| 4.5        | Comparison of the proposed and the existing reversible D-Latches                                                         |     |

|            | with simultaneous $Q$ and $Q'$ output                                                                                    | 88  |

| 4.6        | Comparison of the proposed and the existing reversible Master-                                                           |     |

|            | Slave Flip-Flops. ('-' indicates not calculated)                                                                         | 90  |

| 4.7        | Comparison of the proposed and the existing reversible 2-to-4 decoders                                                   | 91  |

| 4.8        | Comparison of the proposed and the existing reversible 3-to-8 decoders                                                   | 91  |

List of Tables xiii

| 4.9  | Comparison of the proposed and the existing reversible 4:1 multi-         |    |

|------|---------------------------------------------------------------------------|----|

|      | plexer ('-' indicates not calculated)                                     | 92 |

| 4.10 | Comparison of the proposed and the existing reversible $4 \times 2$ RAMs. | 93 |

| 4.11 | Comparison of the proposed and the existing reversible elements of        |    |

|      | reversible Plessey Logic Block in terms of the number of transistors      | 93 |

| 4.12 | Comparison of the proposed and the existing reversible elements of        |    |

|      | reversible Plessey Logic Block in terms of area                           | 94 |

| 4.13 | Comparison of the proposed and the existing reversible elements of        |    |

|      | reversible Plessey Logic Block in terms of power                          | 94 |

| 4.14 | Comparison of the proposed and the existing reversible Plessey            |    |

|      | Logic Block $(4 \times 2)$ in terms of the number of transistors, area    |    |

|      | & power                                                                   | 94 |

## Chapter 1

## Introduction

In 1961, Landauer presented a physical principle [1] of pertaining to the lower theoretical limit of energy consumption. This principle explores that the erasure of a bit consumes KTln2 joules of energy while computing, where, K is the Boltzmann constant and T the absolute temperature at which computation is performed. This energy dissipation is very small (at room temperature  $2.9 * 10^{-21}$  Joules [2]), which is not negligible but noticeable if Moore's law is effective. The historical trend in microelectronics (according to Moore [3]) shows the number of transistor in a dense integrated circuit doubles about every two years. Investigation in [4] also reveals that the lower limit of estimated energy density of a two-dimensional system of binary switches is about 5-10 million  $W/cm^2$  which is much higher than the energy dissipation of sun surface nearly  $6000W/cm^2$ . Hence, with the increasing number of transistor in a single IC, the energy reducing capacity of the IC must be ensured in physical and logical design. Therefore, to keep the trend of scaling in modern ICs, reducing the energy dissipation during computation is getting important. Modern fabrication process and material technologies are trying to reduce the energy dissipation of ICs. In this context, in 1973, Bennett [5] has shown reversible computing would be the future trend to trace the energy dissipation problem as his research proclaims that the reversible computing produces zero energy in ideal cases.

Importance of reversible logic is also comprehensible by its usages in quantum computing which can solve some exponential problem in polynomial time [6, 7] and all the quantum computations are necessarily reversible [6, 8]. Therefore, research on reversible is beneficial to the development of future quantum technologies: reversible design methods might give rise to methods of quantum circuit construction, resulting in much more powerful computers and computations. Besides the quantum technologies [9, 10, 11, 12, 13, 14, 15], some other applications of reversible logic are the optical computing [16, 17], particular adiabatic circuit [18], nanotechnology [19, 20], and DNA technology [16]. These technologies exploit reversible logic to reduce power consumption.

The research on reversible logic is expanding toward both design and synthesis. Several researchers have been exploring techniques for synthesis of reversible logic circuits and many interesting contributions have been made [21, 22, 23, 24, 25, 26, 27]. Authors in [28] propose a bidirectional, transformation based algorithm which can synthesize any reversible logic function with minimum number of constant inputs, by using generalized Toffoli gates. Afterward, authors in [29, 30, 31] present some automated reversible and quantum logic circuit synthesis methods based on genetic algorithm (GA) and evolutionary algorithm (EA). They use the global optimization properties of these algorithm to synthesize reversible and quantum circuits for obtaining near optimal circuits. Recently, in [32, 33], interesting contributions have been made toward deriving exact minimal elementary quantum gate realization of reversible combinational circuits. However, in the synthesis of the reversible logic, only few works address the optimization in terms of delay.

Reversible arithmetic units such as adder, subtractors, multiplier, divider which form the essential components of a computing system have also been designed in binary as well as ternary logic as in [34, 35]. Recent work on reversible sequential

circuits are presented in [36].

On the way of designing circuits in reversible logic, most of the constructed circuits are application specific. This application Specific Integrated Circuit (ASIC) is virtually every type of chip that performs a dedicated task. ASIC has limited usage in industry level for lacking flexibility for changes, expensiveness and difficulty to test and debug. To mitigate these problems, digital industry widely use the programmable devices (PLDs). Zero NRE cost, dense architecture with very high performance improvements make PLDs a very attractive alternative to ASICs. This thesis emphasis on the two major categories of PLD, namely Programmable Logic Array (PLA) and Field Programmable Gate Array (FPGA).

PLA has the advantages in terms of regularity over the other conventional circuits like cascade networks [37, 38, 39, 40]. It ensures an understandable and designable regular circuit. Authors in [38] also ensure that the PLA can be used to design binary valued and multiple-valued logic circuits. Different synthesis methods exist which can realize and minimize the PLA [37, 38, 39]. For example, adders are realized using minimized PLA in [41]. ESOP synthesis in PLA gives out better result than SOP realization [42, 43]. In consequence, authors in [44] propose the reversible wave cascade of ESOP synthesis and authors in [45] propose garbage minimization technique. Besides, authors in [46] [47] and [48] continue their research in ESOP realization.

Over-whelmed opportunities of FPGAs and energy saving characteristics of reversible logic have caught the eyes of the researchers to design the FPGAs in power recurring ways and it leads the design of the reversible FPGAs [49, 50, 51, 52]. Authors in [49] focus on the LUT based logic block of FPGA, whereas, others researches focus on Plessey Logic block of FPGA. Their lacking in generality, scalability and efficiency lead the proposed reversible FPGA.

This thesis propose enhanced design methodologies to design PLA and FPGA with reduce cost matrics.

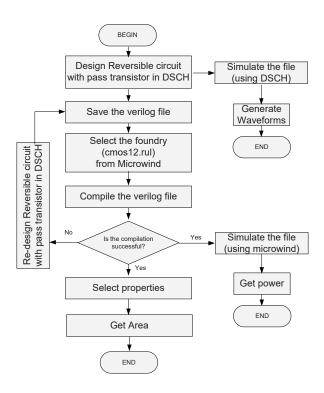

### 1.1 Methodologies of this Research

While working on this research, some important steps are followed:

- Understanding Reversible Logic and recent research trend in Reversible Logic.

Studying on Reversible circuit design procedure, its advantages in creating low power devices over existing irreversible logic design. The basics of quantum computation and quantum circuit synthesis are also studied.

- Understanding the properties and uses of various existing reversible logic gates and construction procedure new gate from the existing one. Studding on how the cost parameters of the reversible circuits are assigned and how the circuits are realized in transistor level.

- Simulation processes of reversible circuits are also studied.

- Understanding Programmable Logic Devices such as PLA, FPGA and then gain knowledge to implement the existing Programmable Logic Devices in reversible way.

- Developing the idea for logic synthesis mechanism in reversible Programmable Logic Devices and design the individual components of reversible FPGA.

- Experiment the proposed circuits with some of the popular simulation mechanisms to make a comparison of the new method with the existing methods.

### 1.2 Challenges of this Research

The synthesis methods of reversible logic circuits are quite different from the synthesis methods of irreversible logic circuits. Two restrictions on reversible logic synthesis must be followed [53]:

- The fanout of a logic gate must be one.

- A combinational reversible network has to be loop-free.

The first restriction is listed because a fanout structure is not reversible. To cope up with this problem, we use the Feynman gate and Feynman double gate in this thesis. As reversible combinational function is necessarily a finite one-to-one function, the second restriction is considered when reversible circuits are designed. To overcome this restriction in designing reversible sequential circuit, researchers want to assure that the transition function of sequential circuit is constructed by reversible logic [54].

The primary design criteria for efficient reversible logic synthesis are as follows:

- The reversible circuits maximize the gate utilization and thus minimize the number of gates.

- They use as many outputs of every gate as possible, and thus minimize the garbage outputs.

- Efficient circuits also ensures the minimization of quantum cost and delay.

- The reversible circuits should take minimum area and consume less power.

#### 1.3 Contributions of this Research

In this dissertation, we have designed different reversible logic circuits associated with the Reversible Programmable Logic Array and the Reversible Plessey Logic Block of FPGA. We have also proposed design methodology to address the above

important points regarding reversible logic. The dissertation has the following contributions toward the design and synthesis of reversible logic circuits regarding PLA and FPGA.

• The first contribution of this dissertation is the design of three new reversible gates namely the TB (Tara-Babu) gate, HNF (Hafiz-Naz-Flip-Flop) gate, and HND (Hafiz-Naz-Decoder) gate.

The proposed reversible TB gate is a universal gate as it can implement all basic boolean functions (AND, OR, NOT Ex-OR) by using one TB gate and compound functions (NAND and NOR) by using two cascaded TB gates. In this dissertation, we use this gate to realize multi-output ESOP (Exclusive-OR Sum of Product) functions. Quantum cost of the proposed TB gate is 4 and the delay of this gate is  $4\Delta$  which are the least in the literature for generating two AND terms simultaneously.

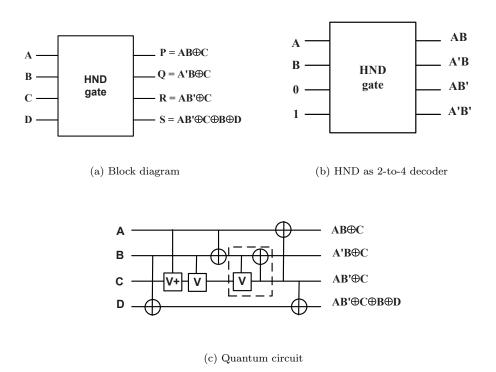

We propose the reversible HNF (Hafiz-Naz-Flip-Flop) gate to design different sequential circuits like D-Latch and reversible Master-Slave Flip-Flop and HND (Hafiz-Naz-Decoder) gate to design reversible Decoder circuit. These two gates are also efficient in terms of the parameters such as garbage outputs, quantum cost and delay.

Construction of a new gate and its quantum circuit is a challenge in reversible logic synthesis as there is no specific guideline. Toffoli or Fredkin synthesis do not give the optimal result all the time. Besides, quantum circuit generation for proposed gate is also laborious. In this thesis we have done this successfully.

• The second contribution is the design of reversible Programmable Logic Array. We have developed of two heuristic algorithms, one is to sort and realize the product terms of ESOP functions and another is to reorder the output

functions. We have simulated the circuits and analyzed the performance of PLAs constructed by the proposed algorithms. The design procedure ensure the proposed circuits are efficient in terms of the number of gates, garbage outputs, and quantum cost.

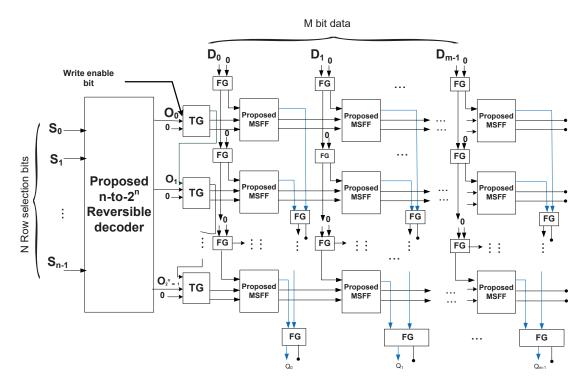

• The third and the final contribution of this dissertation is the design of reversible Field Programmable Gate Array (FPGA). The significant part of the FPGA is the array of logic blocks which execute the basic logical and arithmetic calculations. Hence, this thesis emphasises on the design of the Plessey logic block of FPGA. On the way to design reversible FPGA, a set of different reversible combinational circuits such as decoder, multiplexer, NAND unit as well as different sequential circuits such as reversible D-Latch, reversible Master-Slave Flip-Flop, and reversible RAM are designed. Then, the Plessey logic block is constructed by incorporating all of these proposed components. The designs are optimal in terms of number of garbage outputs as well as quantum cost and delay. We have also computed the number of transistors, the area requirement and the power consumption of the proposed components and then compared with the existing counterparts which also show the efficiency for each individual case.

We expect that the proposed work will encourage a new paradigm of designing programmable devices based on reversible logic.

### 1.4 Organization of the Dissertation

We organize the dissertation as follows.

In **Chapter 2**, theoretical aspects of reversible logic are described. Notations, essential definitions, examples and analysis methods are presented here which are associated with reversible logic theory as well as the architectural theory of programmable logic devices.

Chapter 3 focuses on the efficient design of Reversible Programmable Logic Array (RPLA) for ESOP functions. An introduction regarding Programmable Logic Array covers the architectural issues of the device. Then, previous work on RPLA is analyzed and summarized to point out the weaknesses of previous approaches. Proposed section also discusses the procedures to mitigate the problems of the previous designs.

Then the **Chapter 4** illustrates on efficient Reversible Plessey Logic Block of FPGA. This chapter also describe the theoretical aspects of FPGA, indicate the limitation of previous reversible Plessey Logic Block of FPGA and its components. Finally, it discusses the design procedure to enrich the design of reversible Plessey Logic Block of FPGA.

The dissertation concludes in **Chapter 5** which summarizes the contributions described in this thesis and gives some directions of the further research in the reversible logic area and the reversible programmable devices.

## Chapter 2

## **Background Studies**

#### 2.1 Introduction

The underneath component of the digital computer is a digital circuit whose behavior is expressed as the binary function comprise with binary variables. Each of these variables has only one truth value '0' or '1' but not both and follows the rules of Boolean algebra. A binary function (Boolean function) can be represented in many ways, among them the truth table method is the simplest one. Let a Boolean function F has n variables  $x_1, x_2, x_3, \ldots, x_n$  then the truth table will be as follows:

It is to note that the truth table for single function with n input variables has

Table 2.1: Truth table method

| $x_1$ | $x_2$ | $x_3$ | f |

|-------|-------|-------|---|

| 0     | 0     | 0     | 0 |

| 0     | 0     | 1     | 0 |

| 0     | 1     | 0     | 1 |

| 0     | 1     | 1     | 1 |

| 1     | 0     | 0     | 1 |

| 1     | 0     | 1     | 0 |

| 1     | 1     | 0     | 1 |

| 1     | 1     | 1     | 1 |

n+1 columns and  $2^n$  rows.

**Example 1.** For 3-input 1-output the truth values of the function are shown in Table 2.1.

A multiple output function can also be represented by the truth table having  $2^n$  rows representing the inputs and (n+m) columns, where n is the number of input variables and m is the number of output variables.

**Example 2.** The 3-input 3-output multiple output Boolean function given in Table 2.2.

Table 2.2: Truth table for a 3-input 3-output function

| $x_1$ | $x_2$ | $x_3$ | $f_1$ | $f_2$ | $f_3$ |

|-------|-------|-------|-------|-------|-------|

| 0     | 0     | 0     | 0     | 0     | 0     |

| 0     | 0     | 1     | 0     | 0     | 1     |

| 0     | 1     | 0     | 0     | 1     | 0     |

| 0     | 1     | 1     | 0     | 1     | 1     |

| 1     | 0     | 0     | 1     | 0     | 0     |

| 1     | 0     | 1     | 1     | 0     | 1     |

| 1     | 1     | 0     | 1     | 1     | 1     |

| 1     | 1     | 1     | 1     | 1     | 0     |

The main object in reversible logic theory is the reversible function. The multiple output Boolean function  $F = x_1, x_2, x_3, \dots, x_n$  of n Boolean variables is called reversible if:

- 1. the number of outputs is equal to the number of inputs;

- 2. there is a unique one to one and onto relation between inputs and corresponding outputs. In other words, reversible functions are those that perform permutations of the set of input vectors.

**Example 3.** A 2-input 2-output function given by formula  $f_1 = x_1$ ,  $f_2 = x \oplus y$  is reversible. The correctness of this statement can be verified by analyzing the Table 2.3.

Table 2.3: Reversible function computing the logical Ex-OR

| X | У | X | $x \oplus y$ |

|---|---|---|--------------|

| 0 | 0 | 0 | 0            |

| 0 | 1 | 0 | 1            |

| 1 | 0 | 1 | 1            |

| 1 | 1 | 1 | 0            |

**Example 4.** A 2-input single output function given by formula  $f_1 = x \oplus y$  is not reversible, since it is not an n-input n-output function. However, it can easily be made reversible by adding output x as given in Example 3.

**Example 5.** A 2-input 2-output function given by formula  $f_1 = x$ ,  $f_2 = x.y$  is not reversible also. Though it is an n-input n-output function, there is no unique input-output mapping. This statement can be verified by analyzing the Table 2.4. The two input combinations (0,0) and (0,1) have the same output combination (0,0). In this case, additional input and output are required to make the function reversible.

Table 2.4: Reversible function computing the logical AND

| X | У | X | x.y |

|---|---|---|-----|

| 0 | 0 | 0 | 0   |

| 0 | 1 | 0 | 0   |

| 1 | 0 | 1 | 0   |

| 1 | 1 | 1 | 1   |

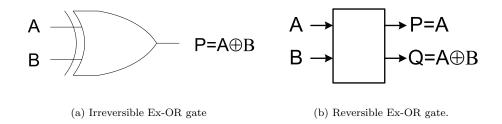

The functions are represented by the small unit of circuit called gate. An irreversible Ex-OR gate is shown in Fig. 2.1 (a), where A, B and P are the inputs and outputs respectively, whereas, a reversible Ex-OR gate (which is Feynman gate) is shown in Fig. 2.1, where (A, B) and (P, Q) are the inputs and outputs respectively and P = A,  $Q = A \oplus B$

Fig. 2.1: Ex-OR function representations by block diagram and logical symbol.

### 2.2 Basic Definitions in Reversible Logic

In this section, we present the definition of the reversible gates and their uses, quantum cost, the challenges of designing reversible circuits, delay computation in reversible circuits.

#### 2.2.1 Reversible Gate

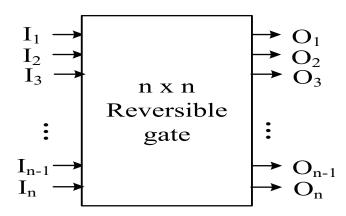

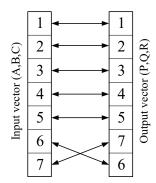

Reversible gate [53] is the unit of the reversible circuit. It holds the property of a bijection function, i.e., both the one-to-one and onto relationship between the inputs and outputs vector are present so that the output can be easily retrive from the unique output for each input. Let, the input vector be  $I_v$ , output vector  $O_v$  and  $I_v = (I_0, I_1, I_2, \ldots I_{n-1}, I_n)$  and  $O_v = (O_0, O_1, O_2 \ldots O_{n-1}, O_n)$ . For each particular input, there exits the relationship  $I_v \leftrightarrow O_v$ .

Fig. 2.2:  $n \times n$  reversible gate

**Example 6.** Fig. 2.2 shows the block diagram of the  $n \times n$  reversible gate.

**Example 7.** For a specific example, let consider the NOT gate, the only conventional gate which is reversible by its nature. The truth table of NOT gate is shown in Table 2.5, which shows that the output 1 comes from the input 0 and the output 0 comes from the input 1, thus the unique input-output patterns are hold.

Table 2.5: Truth table of NOT gate

| Input | Output |

|-------|--------|

| 0     | 1      |

| 1 1   | 0      |

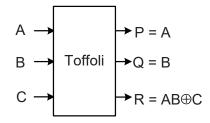

Fig. 2.3: Block diagram Toffoli gate.

Table 2.6: Truth table of reversible Toffoli gate

| Input |   |   |       | Output |                   |  |

|-------|---|---|-------|--------|-------------------|--|

| A     | B | C | P = A | Q = B  | $R = AB \oplus C$ |  |

| 0     | 0 | 0 | 0     | 0      | 0                 |  |

| 0     | 0 | 1 | 0     | 0      | 1                 |  |

| 0     | 1 | 0 | 1     | 1      | 0                 |  |

| 0     | 1 | 1 | 1     | 0      | 0                 |  |

| 1     | 0 | 0 | 1     | 0      | 1                 |  |

| 1     | 0 | 1 | 1     | 1      | 1                 |  |

| 1     | 1 | 0 | 0     | 1      | 1                 |  |

| 1     | 1 | 1 | 0     | 1      | 0                 |  |

Fig. 2.4: Bijection properties of Toffoli gate.

**Example 8.** Fig. 2.3 shows the block diagram of the most popular reversible Toffoli gate. Table 2.6 shows the truth table of this gate. Therefore, Fig. 2.4 reveals the bijection relationship collecting the information from the Toffoli's truth table.

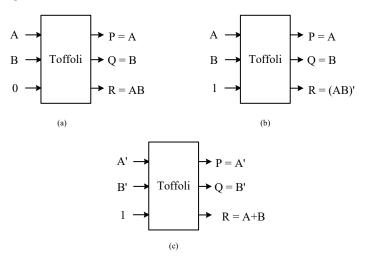

The Toffoli gate plays an important role in reversible logic synthesis. The most importantly, it is a universal gate which functions as any type of gate, such as, AND gate, OR gate, NAND gate, and etc. Fig. 2.5 represents three basic functions of a universal gate.

Fig. 2.5: Universal properties of Toffoli gate.

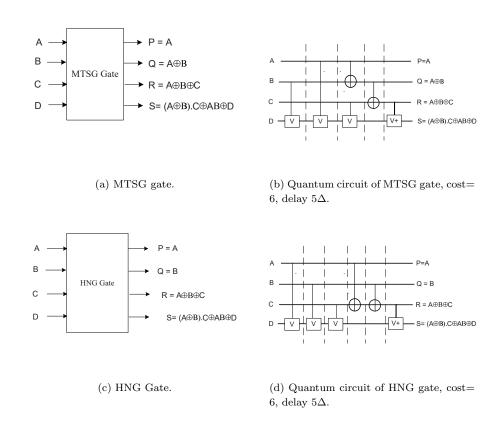

The reversible gates are not uniform in terms of number of input-output, rather than they are constructed such a fashion that they can represent one or more specific function. Therefore, there are a variety of reversible gate in the literature, such as, Feynman gate [55], Feynman Double gate [55], Toffoli gate [53], Fredkin gate [53], Peres gate [56], Modified Fredkin gate [57], HNG gate [58], MTSG gate [59], etc.

#### 2.2.2 Garbage Output

Garbage output is an additional output that makes an n-input and m-output function reversible [53].

**Example 9.** Fig. 2.3 shows the block diagram of Toffoli gate. In case of performing only one AND operation, the outputs P and Q are the garbage outputs.

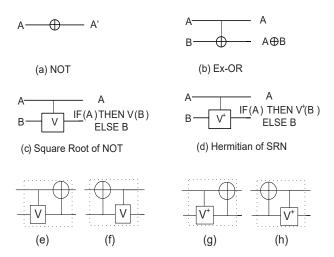

#### 2.2.3 Quantum Cost

Quantum cost is the cost associated with every reversible gate [9, 60]. Every reversible gate has a corresponding quantum circuit which is the combination of the basic quantum gates: NOT, V,  $V^+$  and Ex-OR (CNOT) gate, where, V is a square-root-of NOT gate and  $V^+$  is V's Hermitian. Fig. 2.6(a)-(d) represent all

Fig. 2.6: Basic quantum gates and their symmetric patterns.

of the four basic quantum gates, respectively. Each of these basic gates and their symmetric patterns (Figure 2.6 (e)-(h)) has unit cost [9, 61, 62]. The quantum cost

of a reversible gate is the accumulated number of basic gates and their symmetric patterns in the corresponding quantum circuit.

Fig. 2.7: Quantum circuit of Toffoli gate.

**Example 10.** Fig. 2.7 shows the quantum circuit of the reversible Toffoli gate. It shows the Toffoli gate has the quantum cost 5.

Quantum cost is one of the major cost parameters of the reversible circuit as it relates with the physical implementation cost of that circuit [62]. In designing a perticular circuit, lower value of quantum cost indicates the efficiency of that design. Example 11 can clear this.

Fig. 2.8: Reversible full-adder1 (a) Block diagram (b) Quantum circuit.

**Example 11.** Fig. 2.8(b) and Fig. 2.9(b) shows two quantum circuits of the reversible full-adder having quantum cost 17 and 8, respectively. The later one has less quantum cost, hence more efficient.

Fig. 2.9: Reversible full-adder2 (a) Block diagram (b) Quantum circuit.

Fig. 2.10: Rules in minimization of quantum circuit.

Minimization of quantum cost is desirable in reversible logic design and for this reason the researchers give importance in reduction of quantum cost as possible. There are several works [9, 61, 62] have been done to simplify the quantum circuit and reduce the cost of the circuit. Fig. 2.10(a)-(c) show some templates to reduce the quantum cost, whereas, Fig. 2.10(d)-(e) show some properties of V and  $V^+$  gate. Section 2.2.5 shows the quantum circuits of some existing gates and the quantum circuits of the proposed gates are shown in the respective proposed

sections (TB gate in Section 3.5.1, HNF gate in Section 4.6.1 and HNF gate in Section 4.6.3).

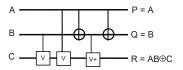

#### 2.2.4 Delay

Delay is an important issue in the design of any circuit. In some earlier research [46, 59] the number of the reversible gates  $(2 \times 2, 3 \times 3 \text{ or any order})$  in the critical path is considered as a unit delay irrespective of their computational complexity. According to this concept, the delay of full-adders of Fig. 2.8(a) Fig. 2.9(a) are same, i.e. 2. However, it is not fair as the number of input and output and the arrangement of the quantum gates in the quantum circuit vary.

Example 12. The block diagrams and quantum circuits of another two full-adders are shown in Fig. 2.11 for delay assessment. Comparison between this Fig. 2.11 with Fig. 2.9 reveals that the construction procedure of a full adder varies not only in terms of number of gate but also on the gate's dimension. Full-adder in Fig. 2.9(a) has two Peres gate, each of which is a three input-output gate, on the other hand, each of the Full-adders in Fig. 2.11(a)& (c) has one reversible gate, which are four input-output gates.

Based on this concept, some researcher considers the logical depth as a measure of the delay [36, 63]. Here, the delay of each  $1 \times 1$  gate and  $2 \times 2$  reversible gate is taken as unit delay and denoted as  $\Delta$ .

**Example 13.** The full-adder using NG gate( 2.8(b)) has delay  $18\Delta$ , on the other hand, each of the full-adder using Peres gate( 2.9(b)), MTSG gate( 2.11(b)) and HNG gate( 2.11(d)) has delay  $8\Delta$ ,  $6\Delta$  and  $6\Delta$ , respectively.

As any  $n \times n$  reversible gate can be designed from  $1 \times 1$  reversible gates and  $2 \times 2$  reversible gates, such as CNOT gate, Controlled-V, and Controlled- $V^+$  gates, the delay of a  $n \times n$  reversible gate can be computed by calculating its logical depth when it is designed from smaller  $1 \times 1$  and  $2 \times 2$  reversible gates. Still, the quantum cost and delay are not same though they may have same quantitive value.

Fig. 2.11: Delay assessment of reversible gates.

**Example 14.** The block diagrams and quantum circuits of MTSG gate and HNG gate of Fig. 2.11 for delay shows that the quantum cost of MTSG gate is 6 and the delay is  $5\Delta$ . On the other hand, the quantum cost of HNG gate is 6 and the delay is  $6\Delta$ .

#### 2.2.5 More about Reversible Gates

Reversible circuits consist of a group of reversible gates. There are several reversible gates in the literature. Some of the reversible gates are described in this section.

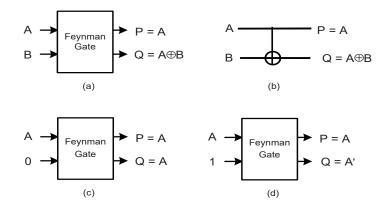

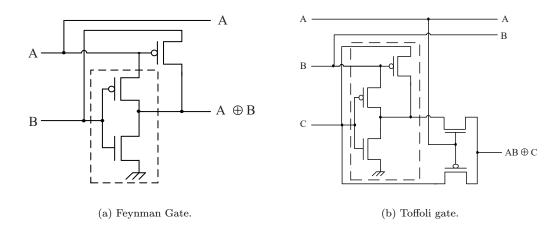

#### 2.2.5.1 Feynman Gate (CNOT Gate or Ex-OR Gate)

The Feynman gate (FG) [55] is a 2-input 2-output reversible gate which has the input-output pattern as follows,

$$(A, B) \leftrightarrow (P = A, Q = A \oplus B)$$

where, A, B denote the input variables and P, Q denote the output variables, respectively. Fig. 2.12(a) and (b) show the block diagram and the quantum circuit of the Feynman gate, respectively. As the quantum circuit of Feynman Gate has only one Ex-OR gate, the quantum cost of FG is 1 and delay is 1  $\Delta$ .

Other than as an Ex-OR gate, the Feynman gate copies the input to avoid the fanout problem in reversible logic (Fig. 2.12(c)). Besides, it generates the complement of an input (Fig. 2.12(d)).

Fig. 2.12: Feynman gate

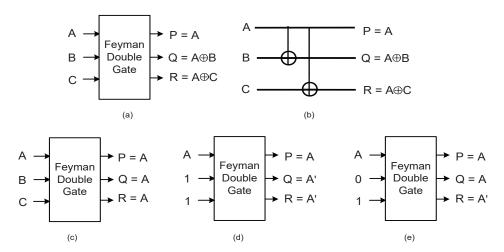

#### 2.2.5.2 Feynman Double Gate (F2G)

The Feynman double gate (F2G) [55] is a 3-input 3-output reversible gate which has the input-output pattern as follows,

$$(A, B, C) \leftrightarrow (P = A, Q = A \oplus B, R = A \oplus C)$$

where, A, B, C denote the input variables and P, Q, R denote the output variables, respectively. Fig. 2.13(a) and (b) shows the block diagram and the quantum circuit of the Feynman double gate, respectively.

F2G is a combination of two FG gates. Like the FG, it also serves the purpose of copying (Fig. 2.13(c)) and generating the complement of the inputs (Fig. 2.13(d)). It has quantum cost 2 and delay  $2\Delta$ .

Fig. 2.13: Feynman Double gate

#### 2.2.5.3 Toffoli Gate (TG)

Though the decription of Toffoli gate is ilustrated earlier in Section 2.2.1, the formal definition is given here. A Toffoli Gate (TG) [53] is a 3-input 3-output reversible gate which has the input-output pattern as follows,

$$(A, B, C) \leftrightarrow (P = A, Q = B, R = AB \oplus C),$$

$A,\ B,\ C$  denote the input variables and  $P,\ Q,\ R$  denote the output variables, respectively. Fig. 2.3 and Fig. 2.7 show the block diagram and the quantum circuit of the TG, respectively. Quantum circuit of TG needs two Controlled-V gates, one Controlled- $V^+$  gate and two Ex-OR gates to implement it and all the basic gates are serially placed. As a result, the quantum cost of Toffoli gate is 5 and delay of Toffoli gate is  $5\Delta$ .

Fig. 2.14: Popular reversible gates.

As the Toffoli gate is a universal reversible gate, it has a great importance in reversible logic synthesis.

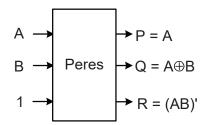

#### 2.2.5.4 Peres Gate (PG)

A Peres gate (PG) [56] is a 3-input 3-output reversible gate which has the inputoutput pattern as follows,

$$(A, B, C) \leftrightarrow (P = A, Q = A \oplus B, R = AB \oplus C),$$

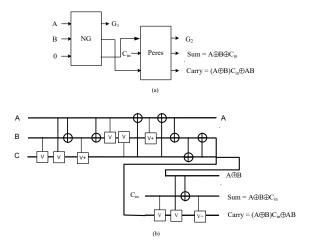

where, A, B, C denote the input variables and P, Q, R denote the output variables, respectively. Fig. 2.14(a) shows the Peres gate [56] and Fig. 2.14(b) shows the quantum circuit of the Peres gate (PG).

Peres gate requires two Controlled- $V^+$  gates, one Controlled-V gate and one Ex-OR gate in its quantum circuit, therefore, the quantum cost of Peres gate is 4. Actually, Peres Gate is the combination of Feynman Gate (FG) and Toffoli Gate (TG) and Peres gate can simultaneously generate two output functions (from Q and R). This gate is popular to construct the full-adder circuits or other circuits which require an Ex-OR operation and the operations done by Toffoli gate, even with the lower cost than that of Toffoli gate.

#### 2.2.5.5 Fredkin Gate (FRG)

A Fredkin gate (FRG) [53] is a 3-input 3-output reversible gate which has the input-output pattern as follows,

$$(A,B,C) \leftrightarrow (P=A,Q=A'B \oplus AC,R=AB \oplus A'C)$$

where, A, B, C denote the input variables and P, Q, R denote the output variables, respectively.

Fig. 2.14(c) and Fig. 2.14(d) shows the block diagram and the quantum circuit of Fredkin gate, respectively.

Quantum circuit of Fredkin gate consists of two dotted rectangles, one Controlled-V gate, and two Ex-OR gates. Thus, the quantum cost of Fredkin gate is 5. Each basic gates and symmetric patterns of those gate (Fig. 2.6 (e)-(h)) has unit cost and unit delay. The arrangement of the basic quantum gates and their symmetric patterns estimates the delay of Fredkin gate  $5\Delta$ .

Fredkin gate also has its importance in reversible literature for generating one output is direct as input and two other outputs as two different Boolean functions. It is also called SWAP gate, as, if the first input is 1, the other two inputs swap in the output. Another use of Fredkin gate is to construct the multiplexer circuits [57].

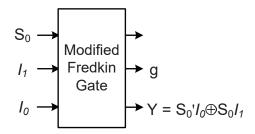

#### 2.2.5.6 Modified Fredkin Gate (MFRG)

A Modified Fredkin (MFRG) gate [57] is a 3-input 3-output reversible gate which has the input-output pattern as follows,

$$(A, B, C) \leftrightarrow (P = A, Q = A'B \oplus AC', R = AB \oplus A'C)$$

where, A, B, C denote the input variables and P, Q, R denote the output variables, respectively. Fig. 2.14(e) and Fig. 2.14(f) are the block diagram and the quantum circuit of Modified Fredkin (MFRG) gate, respectively. It is actually, the modified version of 3-input 3-output Fredkin gate. When A=0, it does the same as Fredkin gate.

Modified Fredkin gate consists of two dotted rectangles, one Controlled-V gate, and one CNOT gates. Hence the quantum cost of Modified Fredkin gate is 4. The arrangement of the quantum gates and their symmetric patterns in the quantum circuit causes the delay of Modified Fredkin (MFRG) gate is  $4\Delta$ .

## 2.3 Physical Implementation Methodologies of Reversible Logic Circuits

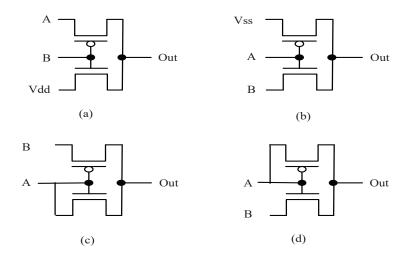

Physical implementation of the reversible circuit plays a role to validate the circuit's construction and its working principles. Among the implementation techniques in literature, Charge Recovery Logic (CRL) is based on the explicit reversible pipelined logic gates [64], whereas, Split-level Charge Recovery Logic (SCRL) is based on split-level voltages [65]. Several other implementation techniques are Energy Recovery Logic (RERL) for ultra-low-energy consumption [66, 67] and nMOS Reversible Energy Recovery Logic (nRERL) [68]. The nanoelectronic and optoelectronic implementations of reversible gates are described in [17, 69]. Besides, authors in [57, 70, 71, 72, 73] use a relatively new and extensively used idea which is Transistor Level Realization of reversible circuits.

Authors in [72] describe several approaches for transistor level realization of basic AND and OR operations. One possible way for implementing two transistors AND or OR gate with VDD and GND (Fig. 2.15 (a) and (b)). This paper also describe AND or OR without any VDD and GND (Fig. 2.15 (c) and (d)).

Fig. 2.15: Transistor level realization of AND and OR gate.

Authors in [72] shows the transistor level realization of reversible four-transistor Fredkin gate and six-transistor Toffoli. Later on, authors in [74] presents an improved version of transistor level realization of reversible gates. The transistor-level realization of Feynman and Toffoli gate according to this designs are in Fig. 2.16 (a), and (b). In this thesis, we follow this design procedure for transistor-level realization of the proposed gates given in the Appendix B.

#### 2.4 Overview of Programmable Logic Devices

Reconfigurability of Programmable Logic Devices makes the prominent use of it in designing digital circuits. A logic gate has a fixed function, whereas, PLD has an undefined function. A PLD has to be programmed before to use it. While designing a digital circuit, a question may arise, which one is preferable to use; logic gates or PLD? Each of these devices has its own complexity such as area, power,

Fig. 2.16: Transistor level realization of reversible gate [74].

density, and implementation cost. Cosequently, the choice will depend on the particular circuit's requirement. Some application use fixed logic gates while other needs consideration. For example, the design of a simple circuit, which requires few logic gates, may be implemented with fixed logic gate, whereas, a complex circuit, considering the complexity, can be developed by using PLD [75]. According to this author, followings are the characteristics and aptitude of programmable logic:

- A PLD is suited for all designs of different size.

- Prototype designs as well as final applicable designs can use the PLDs.

- The designs that might require modification also can use PLDs.

- It is easy to change the designs made by a PLD without changing the circuit hardware and wiring.

- circuits designed by PLDs can use simple tools like the Boolean logic, the Karnaugh map techniques, and the hardware description languages such as VHDL and Verilog HDL.

- Combinational logic designs, sequential logic designs and memory designs,

etc., all suits the PLDs

PLDs have a wide range of application including Glue Logic, State Machines, Synchronization, Decoders, Counters, Bus Interfaces, Parallel-to-Serial conversion, Serial-to-Parallel Conversion, Subsystems and many others. For these extensive varieties of utility, PLD is the right choice for the development and amendment.

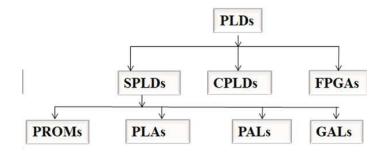

#### 2.4.1 Classification of PLDs

There are variety of PLD both in architecture and functionality. Fig. 2.17 shows a pictorial view of the classification of the PLD. Among the different PLDs, PLA and FPGA are the most popular to construct the circuits. This section has a brief description of these two PLDs.

Fig. 2.17: Classification of the Programmable Logic Devices.

# 2.4.2 The General Architecture of Programmable Logic Array (PLA)

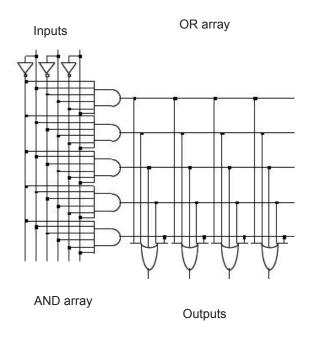

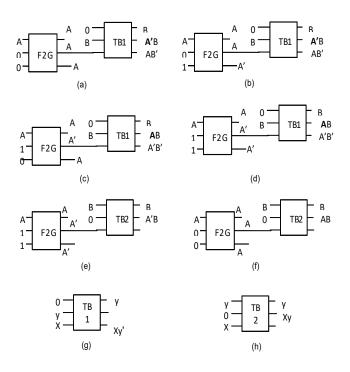

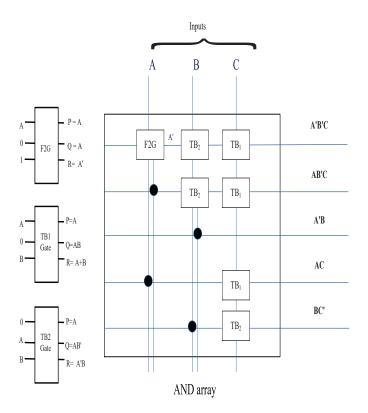

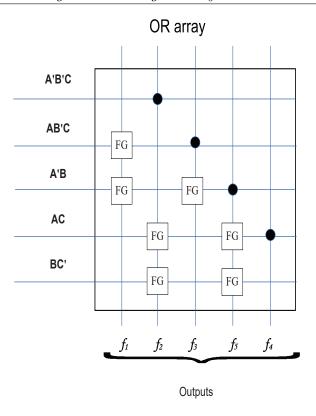

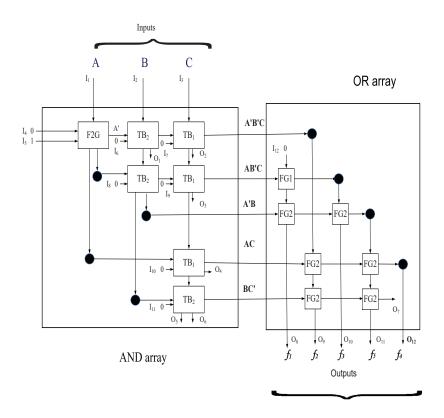

Architecturally, the PLA has two programmable planes: AND-plane and OR-plane (Fig. 2.18(a)).

The AND-plane consists of programmable interconnect along with AND gates. The OR-plane consists of programmable interconnect along with OR gates. In Fig. 2.18(a), there are three inputs to the PLA and three outputs from the PLA. Each of the inputs connects an AND gate with any of the other input by connecting the crossover point of the vertical and horizontal interconnect lines in the AND gate programmable interconnect. Initially, the crossover points are not electrically

(a) AND-OR array.

(b) AND-Ex-OR array.

Fig. 2.18: The architecture of irreversible Programmable Logic Array.

connected, however, configuring the PLA with connects particular crossover points together.

In this figure, the AND gate is connected with a single line to the input. This view is by convention, still, this also means that any of the inputs (vertical lines) can be connected. When the OR-plane Ex-OR, it is called AND-Ex-OR PLA. Fig. 2.18(b) shows the architecture of AND-Ex-OR PLA.

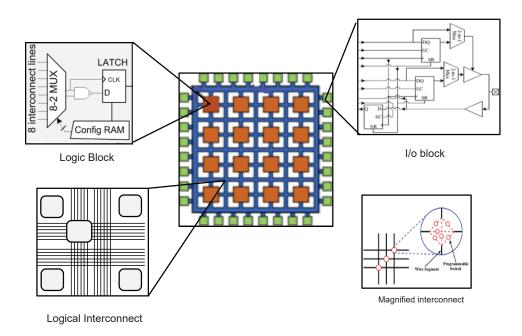

#### 2.4.3 The General Architecture of FPGA

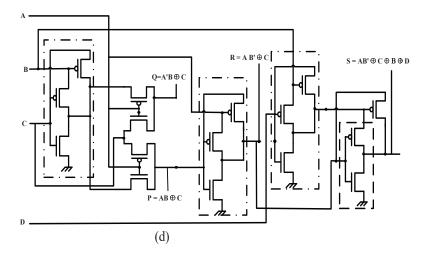

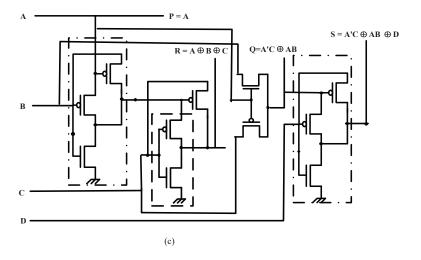

Architecturally, FPGAs consist of an array of programmable logic blocks and a hierarchy of reconfigurable interconnects that allow the blocks to be wired together [76]. Other than the logic block and interconnection, FPGA has input-output blocks for external communication. This logic blocks implements different combinational and sequential logic functions. Manufacturers configure the logic blocks of an FPGA in such a way that they can provide functionality as that of transistor or as complex as that of a microprocessor. The core component of the logic blocks of an FPGA can be a transistor pairs, combinational gates like basic NAND gates or Ex-OR gates, look-up tables, multiplexers or even a wide fan-in AND-OR structure which are connected to each other to implement desired function. Fig. 2.19 shows the architecture of an FPGA with the magnified view of different parts.

As the logic blocks execute the basic logical and arithmetic calculations, they are the most significant parts of an FPGA. There are several type of Logic Blocks in the literature. The Altra Logic Block [77] evolved from the PLA-based architecture consists of wide fan-in AND gates feeding into an OR gate. This configuration has disadvantage as it use pull-up devices that consume static power. An array full of these pull-ups will consume significant amount of power [76].

Fig. 2.19: Different parts of an FPGA.

The advantage of a Look-up tables [78, 79, 80] is that they exhibit high functionality. A K-input LUT can implement any function of K inputs and there are  $2^{2^K}$  such functions, however, they are unacceptably large for more than about five inputs, since the number of memory cells needed for a K-input lookup table is  $2^K$ . Though the number of implementable functions increase very fast, they all are not commonly used in logic designs and are also difficult to exploit for a logic synthesis tool. Hence, there is waste of LUTs.

Though the Actel Logic Block [81, 82] and the Quicklogic Logic Block [83] contain multiplexers which also provide large degree of functionality, they achieve at the expense of a large number of inputs.

However, the Plessey Logic Block [84] (Fig. 2.19) based on NAND unit along with other clusters of components (e.g., Random Access Memories, multiplexers and latches) can overcome the former difficulties [78, 79, 80, 84, 85, 86, 87, 88].

In this thesis, we emphasize on the compactness of the physical architecture of Logic Block and Plessey Logic Block is the right choice.

## 2.5 Summary

This chapter presents a brief study on the basic terminologies on reversible logic. It also includes a short overview on programmable logic devices. Next chapter deals with the design issues of the reversible Programmable Logic Array and then some solutions are proposed to mitigate the deign issues.

## Chapter 3

## Reversible Programmable Logic Array

#### 3.1 Introduction

In the previous chapter, we gave the descriptions of the basic terminologies regarding reversible logic synthesis and programmable logic devices. In this chapter, we explore an efficient design methodology of the reversible Programmable Logic Array (RPLA).

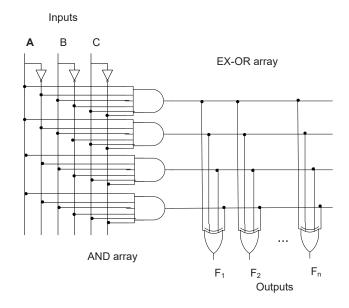

An elegant solution to the mapping of irregular combinational logic function into a regular structure is provided by Programmable Logic Array. This array logic is based on AND, OR and NOT synthesis to implement SOP or POS, whereas reversible logic prefers Ex-OR operation as well as Exclusive Sum-of-Product (ESOP) synthesis. ESOP synthesis gives out better result than SOP realization where many useful methods are proposed for minimizing multi-output Boolean functions into ESOP form [45, 89]. This chapter has proposed a new approach of designing RPLA for ESOP synthesis.

#### 3.2 Contribution

The key contributions of this Chapter are as follows:

- We propose a low cost  $3 \times 3$  reversible universal Tara-Babu (TB) Gate.

- Then we develop a heuristic algorithm to sort and realize the product terms.

- We enables the sharing-property of the internal sub-products by using the proposed algorithm to reduce the number of gates, garbage outputs and quantum cost.

- The proposed algorithm also reorders the output functions to make the circuit optimum.

- Finally, we analyze the performance of the proposed algorithm by using MCNC benchmark functions with compared to other existing designs.

## 3.3 Organization of the Chapter

The organization of rest of the chapter is as follows: in Section 3.4, we explore the existing works in the relevant literature; while Section 3.5.1 proposes the reversible Tara-Babu gate. Then, Section 3.5.2 describes the proposed AND plane, Section 3.5.3 describes the proposed Ex-OR plane and Section 3.6 describes the implementation of the proposed RPLA. We Simulate the proposed circuits and evaluate the performance of the circuits using the proposed algorithm in Section 3.7, whereas, Section 3.8 summarizes the whole chapter.

#### 3.4 Related Works on RPLA

The Boolean function's expression are of three forms, SOP, POS or ESOP form. SOP, POS, and ESOP stand for Sum-of-Products, Products-of-Sum, and Exclusive-Sum-of-Products respectively. A SOP expression is as follows:

$$F_{SOP} = X_1 + X_2 + \dots + X_n \tag{3.1}$$

Where,  $X_i$  is a minterm of one or more literals or product of some minterms, for 1 < i < n.

On the other hand, SOP expression is

$$F_{POS} = Y_1 Y_2 \dots Y_m \tag{3.2}$$

Where  $Y_j$  is a maxterm of one or more literals or sum of some maxterms, for  $1 < j \le m$ .

ESOP stands for Exclusive-OR-Sum-of-Product, which can be expressed as

$$F_{ESOP} = X_1 \oplus X_2 \oplus \dots \oplus X_n \tag{3.3}$$

Where  $X_i$  is a minterm of one or more literals or product of some minterms, for  $1 < i \le n$  and F is Ex-OR-ed with n terms.

**Example 15.** Equation 3.4 shows an example of SOP expression, Equation 3.5 is a POS expression, and Equation 3.6 shows an example of ESOP expression.

$$F_1 = AB' + A'BC' + AC' (3.4)$$

$$F_2 = (A' + B).(A + B' + C)(A' + C)$$

(3.5)

$$F_3 = A'B' \oplus ABC \oplus C' \tag{3.6}$$

Programmable Logic Array realizes the irregular logic function into a regular structure by using both the SOP and ESOP form. However, among all the forms even in, as shown in the example 15, the ESOP is compact and hence cost effective [90, 91]. We can get the ESOP form from the SOP form by using EXORCISM4 [92]. Authors in [90] generate the minimal ESOP and use to synthesize the reversible logic. They wants to take advantage of shared minterms to minimize the garbage outputs. However, in this way, several other minterms cause more garbage outputs. Factorization of ESOP may benefit from this synthesis approach but has penalties regarding the number of gates and garbage outputs. The minimal form of ESOP is also used in [44]. They use a different technique. This technique focuses on rearranging the products in ascending order according to the decimal value of the product terms. Then, an algorithm is provided in which each step consider a configuration of the Toffoli gate. Though this method overcomes the penalties of the method in [90], it suffers from time complexity described in [46]. However, the design in [46] still follows the conventional architecture (both complement and non-complement lines for copying input variables) of Programmable Logic Array.

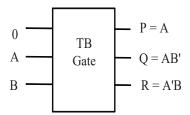

Authors in [47] replace the complement and non-complement lines by one line. This design uses Fredkin gates in AND plane of RPLA for AND operations and F2G in Ex-OR plane of RPLA for Ex-OR operations. Though eliminating of one line makes this design enhance, using these two gates elevates the number of garbage and quantum cost. Parallel research on RPLA in [48] also attempt to design the RPLA which minimize the cost, however, maximize the garbage output than [47].

Analyzing all these, this chapter proposes an efficient RPLA for ESOP synthesis which reduces the cost metrics.

#### 3.5 Proposed RPLA

This section describes the proposed design of Reversible Programmable Logic Array (RPLA). On the way to design the RPLA, this dissertation assumes that the functions are already been minimized and available in ESOP form. Still then, different output functions of multi-output ESOP may have some common products and sub-products. Sharing these products or sub-products in RPLA is advantageous. For this reason, we propose a reversible gate namely Tara-Babu (TB) gate in Section 3.5.1. This gate enables the product-sharing property. Section 3.5.2 describes the proposed method to generate the AND-plane, whereas, Section 3.5.3 focuses on the generation of the Ex-OR-plane. Finally, Section 3.6 describes the implementation of the proposed RPLA with these AND-plane and Ex-OR-plane.

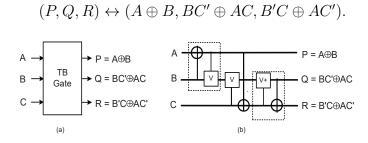

#### 3.5.1 Proposed Reversible Tara-Babu (TB) Gate

This section presents the proposed gate namely Tara-Babu (TB) which we use for the AND operation in AND Plane. Let, A,B,and C are the inputs and P,Q,and R are the outputs of TB gate, then the relationship between inputs and outputs are

FIG. 3.1: Proposed reversible TB gate: (a) block diagram (b) quantum circuit.

Fig. 3.1 (a) and Fig. 3.1 (b) shows the block diagram and the quantum circuit of TB gate, respectively and Table 3.1 proves the reversibility of the proposed gate. Quantum cost of the proposed TB gate is 4 and the delay of this gate is  $4\Delta$  which is the least in the literature for generating two AND terms simultaneously.

|       |   |    |                  | 1 1              | O                    |  |  |

|-------|---|----|------------------|------------------|----------------------|--|--|

| Input |   | .t |                  | Output           |                      |  |  |

| A     | B | C  | $P = A \oplus B$ | $Q=BC'\oplus AC$ | $R = B'C \oplus AC'$ |  |  |

| 0     | 0 | 0  | 0                | 0                | 0                    |  |  |

| 0     | 0 | 1  | 0                | 0                | 1                    |  |  |

| 0     | 1 | 0  | 1                | 1                | 0                    |  |  |

| 0     | 1 | 1  | 1                | 0                | 0                    |  |  |

| 1     | 0 | 0  | 1                | 0                | 1                    |  |  |

| 1     | 0 | 1  | 1                | 1                | 1                    |  |  |

| 1     | 1 | 0  | 0                | 1                | 1                    |  |  |

| 1     | 1 | 1  | 0                | 1                | 0                    |  |  |

|       |   |    |                  |                  |                      |  |  |

Table 3.1: Truth table of the proposed reversible TB gate

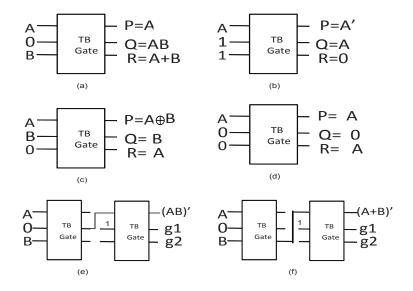

The proposed reversible TB gate is a universal gate as it can implement all basic boolean functions (AND, OR, NOT Ex-OR) by using one TB gate and compound functions (NAND and NOR) by using two cascaded TB gates. Fig. 3.2 (a) shows the utilization of TB gate as AND and OR gates, Fig. 3.2(b) shows the implementation of NOT gate. Afterward, Fig. 3.2(c) presents the Ex-OR function and Fig. 3.2(d) depicts the copy property to solve the fan-out problem. Finally, Fig. 3.2(e) and Fig. 3.2(f) show the NAND function and the NOR function by cascading two TB gates, respectively. Besides, Fig. 3.3 shows the AND terms generated by the TB gate.

Fig. 3.2: Implementation of all boolean functions using the proposed reversible TB gate.

Fig. 3.3: Different AND terms produced simultaneously by the proposed TB gate.